IBM, en colaboración con Samsung, ha conseguido desarrollar lo que será el futuro de los chips semiconductores, con una nueva estructura de transistores y nuevos materiales para mejorar el rendimiento y la tolerancia a la electromigración. Estos nuevos transistores se conocen como VTFET, y para las líneas de conexión también se ha incluido el rutenio, junto con el ya conocido cobre (que en su momento sustituyó al aluminio).

¿Qué es VTFET?

Se ha alcanzado un significativo avance en el diseño de semiconductores gracias a la colaboración entre IBM Research, Samsung y nuestro aliado Albany Research Alliance. Nuestra estrategia novedosa, denominada Transistor de Efecto de Campo de Lámina Nanométrica de Transporte Vertical (VTFET o Vertical-Transport nanosheet FET), podría resultar fundamental para mantener vigente la ley de Moore en los próximos años.

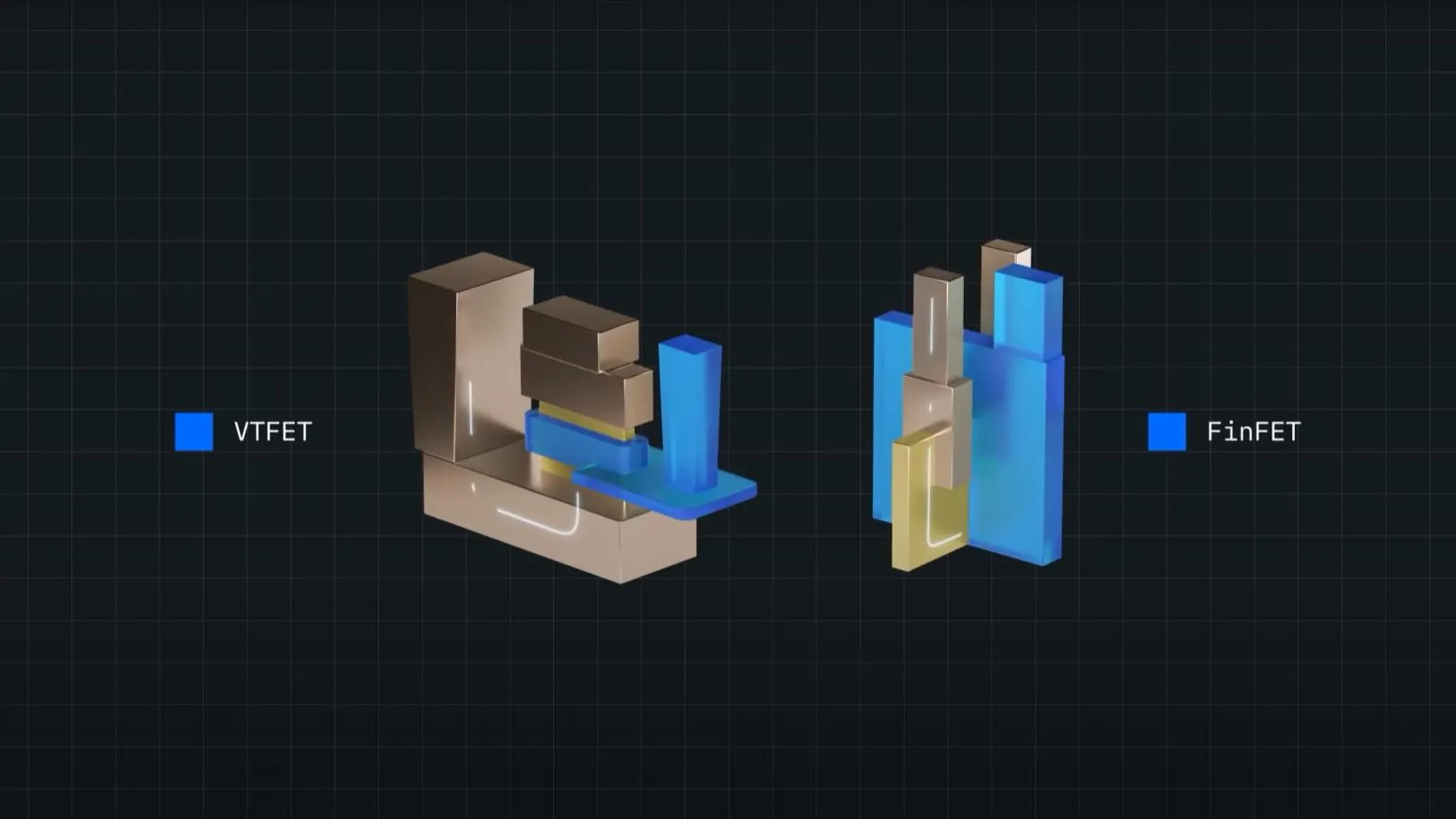

El VTFET representa una revolucionaria arquitectura de los transistores. A diferencia de los modelos convencionales, este innovador transistor emplea finas láminas nanométricas para facilitar el flujo vertical de corriente eléctrica, en contraste con el tradicional flujo lateral. Esto conlleva a un mejor desempeño y una mayor eficiencia en el consumo de energía.

Un aspecto fundamental del VTFET es su capacidad para integrar un mayor número de transistores en un chip, sin que esto implique un incremento considerable en su tamaño. Al posibilitar el flujo vertical de corriente, se logra reducir la distancia que la señal eléctrica debe recorrer, resultando en una optimización de la velocidad y la eficiencia de procesamiento.

Asimismo, el VTFET presenta una mayor resistencia al calor y a las pérdidas eléctricas, lo que lo convierte en una alternativa promisoria para aplicaciones que demandan alto rendimiento y potencia. Esto resulta particularmente relevante en áreas como la inteligencia artificial y el cómputo cuántico, donde se requiere un procesamiento rápido e intenso de grandes volúmenes de información.

El enfoque VTFET desarrollado por IBM Research y Samsung evidencia cómo la constante innovación y la exploración de enfoques nuevos pueden superar los límites tecnológicos presentes. Aunque la ley de Moore podría estar alcanzando su límite en términos de incremento de la cantidad de transistores en un chip, esta tecnología emergente señala un camino prometedor, y las cifras que te comento a continuación así lo avalan.

En el presente, las nuevas configuraciones predominantes de los chips se fundamentan en los transistores de efecto de campo de transporte lateral, como el transistor de efecto de campo de aleta, conocido como FinFET debido a su semejanza con la aleta trasera de un pez. Estos transistores se apilan a lo largo de la superficie de una oblea de silicio.

En contraposición, el VTFET organiza los transistores en una disposición perpendicular a la oblea de silicio y canaliza la corriente eléctrica en dirección vertical a la superficie de la oblea. Esta nueva aproximación aborda los obstáculos del escalado al relajar las restricciones físicas en relación con la longitud de la puerta del transistor, el grosor del espacio entre componentes y las dimensiones de los contactos, de manera que cada una de estas propiedades pueda ser optimizada en términos de rendimiento o eficiencia energética.

A través del VTFET, se ha logrado demostrar de manera exitosa la posibilidad de explotar la escala más allá de la tecnología de los semiconductores CMOS actuales. En estos nodos avanzados, el VTFET podría ofrecer hasta el doble de rendimiento o una disminución de hasta un 85% en el consumo energético en comparación con la alternativa escalada de FinFET. De hecho, IBM anunció una oblea de chips con proceso de 2nm y 50.000.000.000 de transistores en un espacio similar al de una uña de un dedo.

También te puede interesar saber cuáles son los mejores microprocesadores del mercado

En el pasado, los diseñadores incrementaban la densidad de transistores en un chip mediante la reducción del ancho de la puerta y las interconexiones. El espacio físico donde se acomodan todos los componentes se denomina Paso de Puerta Conectado (CGP, por sus siglas en inglés), es decir, la distancia mínima entre las puertas de los transistores. La capacidad para disminuir los pasos de puerta y conexión permitió a los diseñadores de circuitos integrados transitar de miles a millones de transistores en nuestros dispositivos. No obstante, con las tecnologías más avanzadas de FinFET, solo hay cierto margen para espaciadores, puertas y contactos. Una vez que se llega al límite de CGP, no queda espacio adicional.

Al direccionar el flujo de corriente eléctrica en forma vertical, las puertas, espaciadores y contactos dejan de estar restringidos por las modalidades tradicionales. Es decir, hay margen para ampliar el CGP a la vez que se conserva un tamaño adecuado de transistor, contacto y aislamiento (denominado Shallow Trench Isolation o STI).

Al liberarnos de las limitaciones de la disposición lateral y el flujo de corriente, los investigadores también pudieron emplear contactos de fuente/drenaje de mayor tamaño para incrementar la corriente en el dispositivo. La longitud de la puerta puede ser ajustada para optimizar la corriente de conducción y las fugas del dispositivo, mientras que el espesor del espaciador puede ser ajustado independientemente para disminuir la capacitancia. Ya no están obligados a hacer concesiones en relación con el tamaño de la puerta, el espaciador y el contacto, lo que puede conllevar a una mayor velocidad de conmutación y una reducción en el consumo de energía.

Otro aspecto crucial del VTFET es su capacidad para utilizar el STI con el propósito de aislar circuitos adyacentes y lograr un Aislamiento de Rotura de Difusión Cero (ZDB, por sus siglas en inglés), sin perder pasos activos de la puerta. En comparación, la densidad de la disposición FET de transporte lateral se ve afectada por rupturas de difusión doble o simple requeridas para el aislamiento de circuitos, lo cual influye en la posibilidad de seguir reduciendo la tecnología.

Conexiones Cu/Ru/Co/TaN

Hace unas décadas, los primeros chips que se fabricaron se hicieron con interconexiones de aluminio (Al), algo que limitaba bastante la velocidad a la que podían trabajar, entre otras desventajas. En cambio, IBM creó las interconexiones de cobre, y fue pionero en su uso, junto con AMD. De hecho, AMD logró superar la barrera de 1 Ghz de frecuencia de reloj con su K7 (Athlon «Thunderbird») antes que Intel por este motivo.

La nueva tecnología de cobre (Cu) tenía un problema, y es que se consideraba muy «sucia» para una planta de semiconductores, ya que había que realizar un proceso de pulido (CMP) y eso generaba gran cantidad de partículas. Sin embargo, una vez superados estos problemas, se pudo implementar para la fabricación en masa. Esta es la tecnología que ha permanecido hasta la actualidad.

Sin embargo, en la búsqueda incesante de mejoras, también ha habido algunos otros avances en los materiales de conexión o líneas conductoras, introduciendo multitud de elementos nuevos o compuestos para mejorar el rendimiento o reducir algún parámetro perjudicial.

Ahora, IBM también ha constatado una mejora del rendimiento en cuanto a electromigración (EM) en las interconexiones de cobre cuando se utiliza un recubrimiento o liner de rutenio (Ru) y una cubierta de cobalto (Co), y que ésta depende de factores tales como la saturación completa de cobre sin cavidades, el control preciso de la interfaz tanto en la unión y la manipulación del tamaño de grano.

En particular, la migración del cobalto desde la capa superior hacia el revestimiento de rutenio (lo cual causa la escasez de Co en la región superior de las líneas de cobre) se identifica como una de las principales razones detrás de la degradación por electromigración. Con el fin de solucionar este problema, se ha concebido una novedosa variante de recubrimiento de rutenio dopado con cobalto, el cual ha demostrado un incremento notorio en la resistencia a la electromigración al mitigar la difusión del cobalto. Una gran noticia para los nodos de fabricación más avanzados, ya que los procesos de menor tamaño sufrían estos efectos negativos más que los procesos anteriores.

Pero las innovaciones no terminan aquí, IBM también quiere volver a su pasado esplendor en la industria de los semiconductores, cuando era capaz de patentar más cantidad de nuevos avances y tecnologías que sus 10 compañías más inmediatas competidoras.

Ahi que decir que las nuevas interconexiones de cobre con recubrimiento de rutenio dopado se consiguen mediante una reactor de deposición química en fase de vapor (CVD) para las tecnologías de nuevos nodos. Pero estas conexiones necesitaban de barreras te nitruro de tantalio (TaN) que se depositaba mediante pulverización catódica de vapor (PVD). Sin embargo, esta estructura hacía que el espesor del recubrimiento de Ru fuese mayor.

Para disminuir este espesor del Ru se ha sustituido esa tecnología convencional por una estructura bicapa consistente en PVD de tantalio (Ta) y deposición de nitruro de tantalio mediante deposición atómica en capa fina (ALD TaN).

La novedosa configuración de barrera propuesta, conformada por PVD Ta/ALD TaN y un revestimiento delgado de Ru, también ha conducido a una notable mejora en el proceso de pulido químico y mecánico (CMP) del rutenio, al atenuar dos de los desafíos más relevantes en el CMP de Ru:

- El hundimiento del cobre en las líneas estrechas.

- La disparidad en la profundidad de las trincheras entre patrones densos y aislados.

Además, este innovador diseño de barrera con recubrimiento de Ru ha logrado un relleno de cobre sin cavidades, incluso en dimensiones más allá del nodo 7 nm. Por lo tanto, la estructura de revestimiento conformada por PVD Ta/ALD TaN/CVD Ru emerge como una opción altamente prometedora para revestir las interconexiones de cobre en nodos de 7nm en adelante…

¡No olvides comentar!