La tecnología de empaquetado 3D ha llegado para quedarse. Técnicas como 3DFabric de TSMC van a ser la tónica en muchos dispositivos avanzados, más allá de la propia AMD 3D V-Cache. Por eso, merece la pena detenerse y explicar de qué se trata y cómo lo hacen para poder interconectar diferentes chips sin tener que usar interposers como en el caso de los chiplets.

Índice de contenidos

TSMC 3D Fabric

Hace unos años, durante uno de los eventos de TSMC, se dio a conocer una tecnología revolucionaria que permite a sus clientes utilizar empaquetados en tres dimensiones. Esta innovación, llamada 3D Fabric, es un sistema avanzado de empaquetado tridimensional (y también de troqueles en 2.5D) desarrollado por esta importante fundición, que es responsable de la fabricación de marcas como NVIDIA, AMD, Apple, Qualcomm, entre otras. El término «3D Fabric» hace referencia a una estructura de tejido o malla utilizada para conectar de manera interdependiente los diversos componentes del empaquetado.

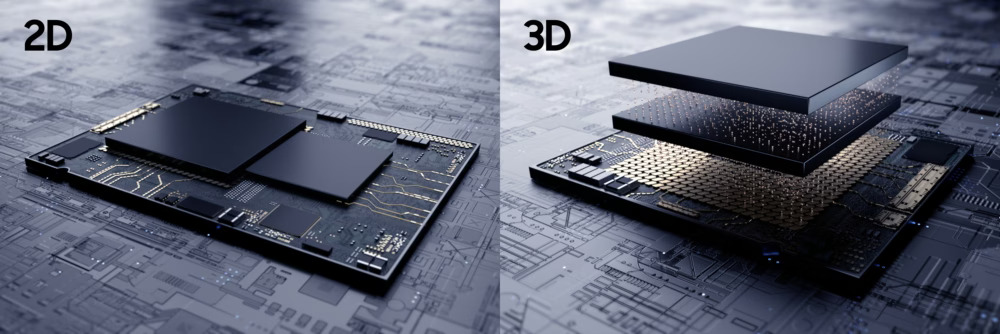

Existen numerosas ventajas en el uso de empaquetados con tecnología 3D Fabric y en configuraciones tridimensionales, ya que permiten integrar una cantidad mucho mayor de chips en un espacio reducido al aprovechar la dimensión vertical. Esto sigue el mismo principio que los rascacielos en comparación con las casas. Sin embargo, no todo son beneficios.

El problema radica en que debido a la alta densidad de chips apilados verticalmente, cada uno de ellos genera calor, lo que implica que las soluciones 3D requieran una mayor capacidad de refrigeración en comparación con los empaquetados convencionales. En algunos casos, puede ser necesario reducir el voltaje o consumo para mitigar estos problemas.

Según las simulaciones realizadas en este tipo de empaquetados, el calor disipado se propaga a través de las TSV o vías que conectan los chips entre sí. Por lo tanto, es crucial tener consideraciones específicas en el diseño de estos chips.

Estas rutas funcionan como una especie de «chimenea», y es importante tenerlo en cuenta al utilizar herramientas EDA (Electronic Design Automation) proporcionadas por los desarrolladores de software a sus clientes. Sin embargo, muchas empresas importantes también emplean sus propias herramientas EDA personalizadas adaptadas a sus preferencias y necesidades. En cualquier caso, estos son puntos críticos que deben tenerse en cuenta durante el diseño antes de enviar el chip a TSMC para su fabricación, y esto también se aplica a otras tecnologías que compiten con la de TSMC y que se mencionarán más adelante.

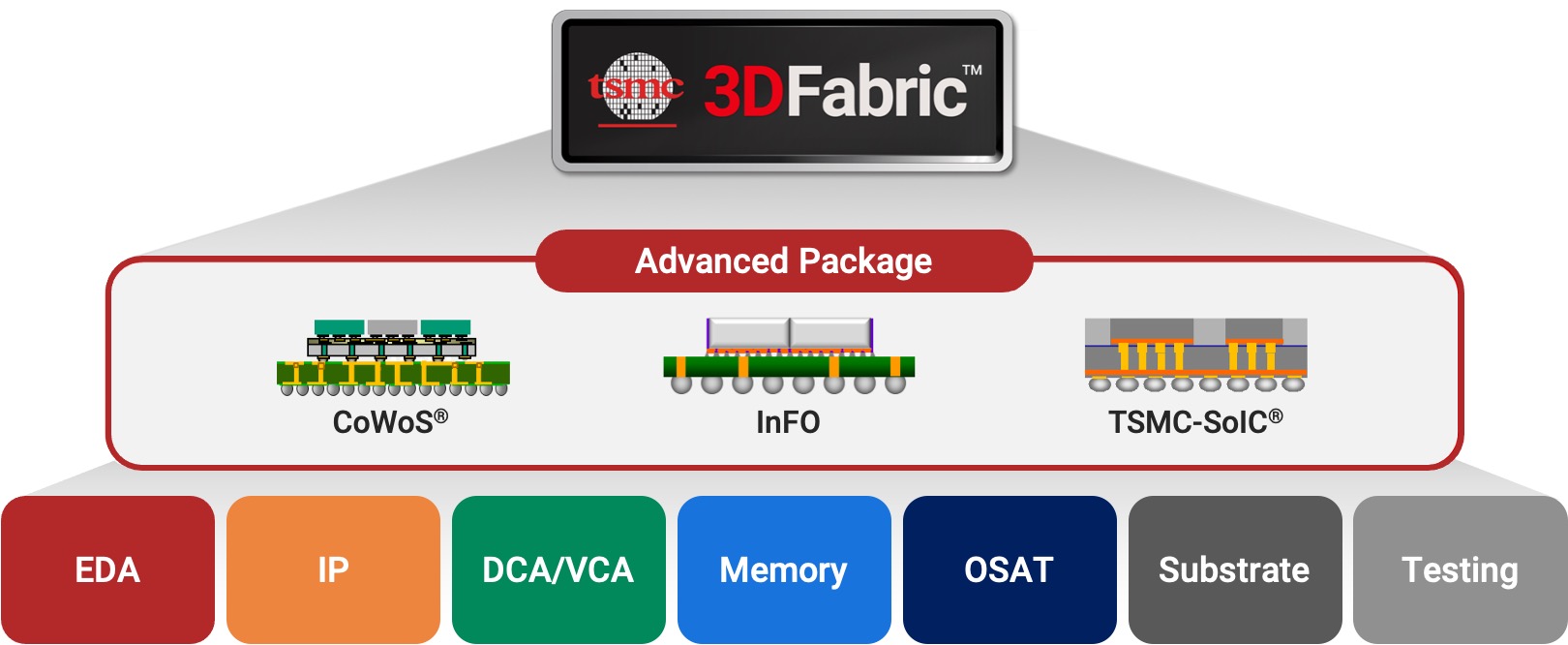

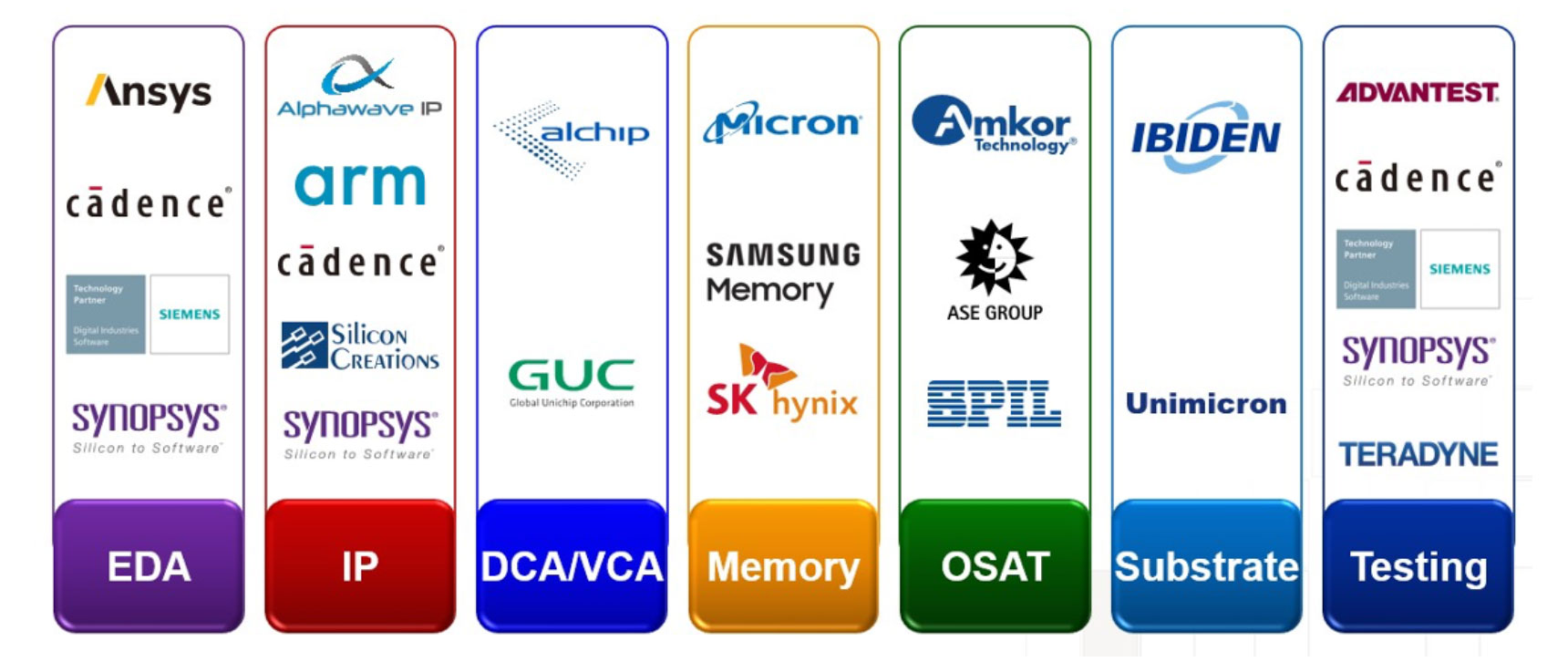

Como puedes apreciar en la anterior imagen, TSMC se ha armado con grandes socios de primer nivel en la industria para poder hacer 3DFabric práctica y posible. Por ejemplo, vemos emprsas como Cadence y Siemens y Synopsys para las herramientas de test, EDA, etc., o sustratos (waferos u obleas) de IBIDEN o Unimicron, memorias de Micron Technologies, Samsung Memory o SK Hynix, chips de procesamiento o lógica IP de otras tantas empresas, etc.

Tecnologías 3D

3DFabric no es una tecnología en sí, sino un conjunto de ellas, como se aprecia en la imagen. Para que todo funcione, se emplean una serie de tecnologías diferentes que hay que conocer, y que son:

- InFO (Integrated FanOut): estos paquetes 2.5D utilizan una oblea modificada con un troquel incrustado invertido y rodeado de compuestos de moldeo. Las capas de redistribución de interconexiones (RDL) se fabrican mediante una oblea de epoxi. En el caso del InFO-L, se refiere a un chiplet que actúa como un puente de silicio entre las matrices o troqueles incrustados en el empaquetado InFO, mejorando la conectividad a través de la metalización RDL.

- CoWoS (Chip-on-Wafer-on-Substrate): esta es otra tecnología utilizada para empaquetados 2.5D, especialmente en pilas de chips de memoria HBM y otras aplicaciones. Se emplean intercaladores con microbumps de enlace y TSV (vías a través del silicio) para lograr una densidad de interconexión mejorada. Además, se ofrecen variantes como el interposer CoWoS-S de silicio, CoWoS-R con tipo RDL, y CoWoS-L con LSI + RDL, para adaptarse a los requisitos de coste y densidad específicos de cada cliente.

- 3D SoIC (System on Integrated Chips): por otro lado, en el empaquetado 3D, encontramos esta tecnología avanzada que forma parte de la 3D Fabric. Está orientada a configuraciones de troqueles cara a cara o cara espalda, utilizando una unión híbrida y conexiones verticales mediante TSV.

También te interesará sabes cuáles son los mejores procesadores con 3D V-Cache

Alternativas

TSMC 3DFabric no es la única tecnología de empaquetado 3D. La competencia también se ha puesto manos a la obra para lanzar sus propias soluciones. Es el caso de las siguientes:

Intel EMIB 3 + Foveros Direct

Durante la reciente presentación de Intel Accelerated, se han revelado avances en el empaquetado de chips que Intel utilizará para mejorar su tecnología Foveros, que ha sido utilizada hasta ahora. Además, se ha anunciado una versión mejorada de EMIB, que estará presente en los próximos procesadores de Intel después de Alder Lake, programados para ser lanzados en octubre próximo.

Desde 2017, EMIB ha liderado la tecnología de interconexión en los chips 2.5D. Los actuales procesadores Intel Xeon para centros de datos, con el nombre en clave Sapphire Rapids, serán los primeros en utilizar la tecnología EMIB, que utiliza conexiones de 55 micras. Además, se ha implementado un diseño de doble retícula que ofrece un rendimiento equivalente a los diseños de una sola retícula. En futuras generaciones, se espera reducir el tamaño de estas conexiones de 55 micras a 45 micras.

La segunda generación de Foveros, que se implementará en los procesadores Intel Meteor Lake, contará con conexiones de 36 micras. Esto se logra aprovechando las capacidades de empaquetado de chips a nivel de oblea. Además de la mejora en el tamaño de las conexiones, la versión mejorada de Foveros permitirá utilizar múltiples nodos tecnológicos, lo que resultará en un amplio rango de TDP, desde 5 hasta 125 vatios.

La GPU Ponte Vecchio para HPC será la primera en utilizar esta nueva generación de Intel Foveros y el EMIB mejorado que se ha utilizado para la producción en masa. La próxima generación de Foveros, presente en los sucesores de Intel Raptor Lake (los Meteor Lake), empleará un nuevo sistema de apilado que brinda máxima flexibilidad para el apilamiento en 3D y permite la interconexión en diseños modulares. Con Foveros Omni, será posible desagregar matrices y combinar las superiores con las inferiores en los procesadores, incluso cuando se utilicen nodos de fabricación diferentes. Esta tecnología estará lista para su implementación en los procesadores Intel Meteor Lake en 2023.

Además de Foveros Omni, Intel utilizará Foveros Direct, que permitirá una conexión directa de cobre a cobre, reduciendo la resistencia y eliminando las limitaciones entre el final de la oblea y el inicio del paquete. Estas conexiones podrán tener un tamaño inferior a 10 micras, lo que permitirá configuraciones de matrices que antes eran imposibles.

Tanto Foveros Direct como Foveros Omni se utilizarán de manera conjunta para lograr una mayor eficiencia y un mejor rendimiento en los nuevos procesadores de Intel que estarán disponibles en 2023. Estas tecnologías han sido desarrolladas en las instalaciones de Intel en Oregón y Arizona, lo que convierte a Intel en la primera y única empresa que realiza estas investigaciones, desarrollo y construcción en territorio estadounidense.

Además, Intel pondrá a disposición de sus clientes esta tecnología de empaquetado 3D a través de su IFS (Intel Foundry Service).

Samsung X-Cube

Samsung Electronics, uno de los principales competidores en el campo de la tecnología de semiconductores junto a TSMC, ha introducido su innovador avance conocido como Samsung X-Cube, que representa el primer desarrollo funcional de silicio en la industria para la creación de SRAM-logic 3D a 7 nm y más allá. Esta tecnología revolucionaria permite ajustar el ancho de banda y la densidad de acuerdo con los requisitos específicos de diseño en aplicaciones emergentes.

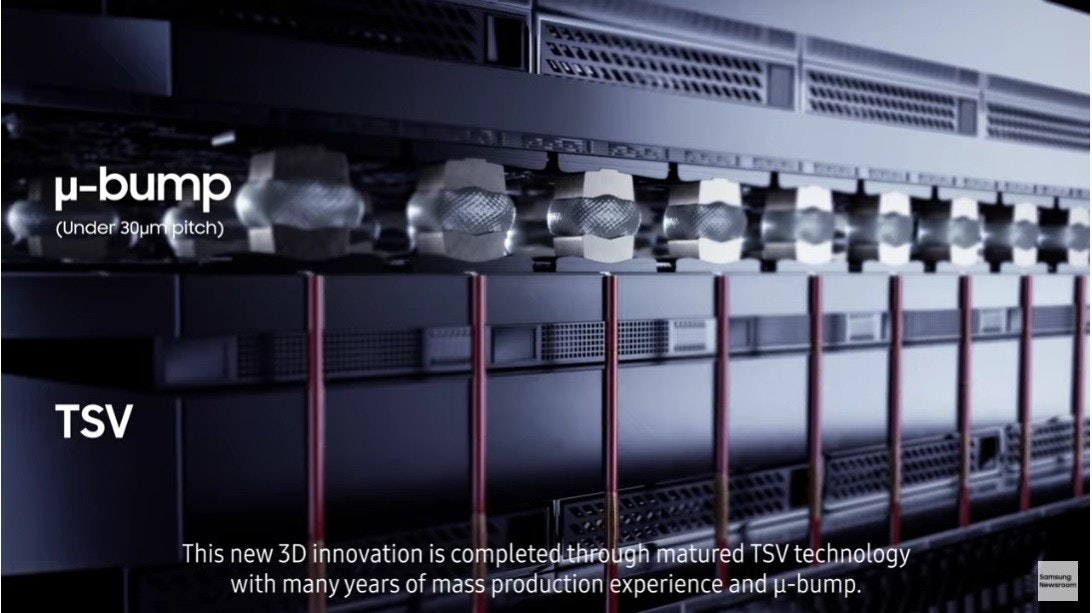

La disponibilidad inmediata de su tecnología de empaquetado tridimensional basada en silicio se produjo un poco después que la de TSMC. Su nombre, X-Cube, proviene de eXtended-Cube y está especialmente diseñada para los nodos de proceso más avanzados del mercado. Aprovechando la tecnología de interconexión a través de silicio (TSV) de Samsung, X-Cube ofrece mejoras significativas en velocidad y eficiencia energética para satisfacer las exigentes demandas de rendimiento en aplicaciones de próxima generación, como 5G, inteligencia artificial, computación de alto rendimiento, así como aplicaciones móviles y dispositivos portables.

Además, esta tecnología, combinada con los nodos más avanzados basados en litografía EUV, logrará un rendimiento superior en una amplia gama de aplicaciones, especialmente en la pila de celdas de memoria SRAM sobre chips lógicos, entre otros. Recordemos que Samsung, junto con SK Hynix y Micron Technologies, es uno de los líderes del sector de la memoria.

Gracias a la integración tridimensional, el diseño del paquete ultradelgado presenta rutas de señal notablemente más cortas entre los chips, lo que maximiza la velocidad de transferencia de datos y la eficiencia energética. Además, los clientes de la fundición de Samsung tienen la opción de escalar el ancho de banda y la densidad de memoria según sus requerimientos específicos. La metodología y el flujo de diseño probados con el silicio de Samsung X-Cube ya están disponibles para los nodos avanzados de 7 nm y 5 nm, y en el futuro, para nodos aún más avanzados. Basándose en este diseño inicial, Samsung planea seguir colaborando con clientes globales sin capacidad de fabricación propia para facilitar la implementación de soluciones 3D IC en aplicaciones de alto rendimiento de próxima generación.

¡No olvides comentar con tus dudas o sugerencias!