Existe una gran preocupación por la memoria actual cuando hablamos de gran escala, como en los sistemas HPC o en los grandes servidores de los centros de datos. En los primeros, uno de los elementos más costosos es la GPU que se usa como acelerador. En cambio, en los servidores más genéricos una de los elementos más costosos es la memoria principal, o memoria RAM. Por eso se están pensando en algunas soluciones para el futuro al respecto, como la tecnología CXL.

Índice de contenidos

¿Por qué esa preocupación por el coste de la memoria RAM?

Si echamos un vistazo atrás, una de las unidades que mayor gasto solía representar hace una década para este tipo de sistemas era la CPU. En muchos casos solía representar hasta la mitad del coste básico de un servidor para un centro de datos, lo que supone una gran inversión cuando se habla de estas grandes infraestructuras con miles de unidades de procesamiento. Algo parecido sucedía en los sistemas HPC de hace unos años, que buscaban potenciar más las unidades de procesamiento y algo menos la memoria RAM.

En estos sistemas, la memoria principal suponía al rededor del 15% del coste del servidor, con un 10% para la placa base y entre el 5-10% para la memoria secundaria, es decir, los medios de almacenamiento no volátiles. Mientras en algunos casos la interfaz de red y otros elementos ya se incluían en la placa base, en los sistemas con Ethernet avanzada o InfiniBand se tenía que agregar un coste extra para estas redes de alto rendimiento y los equipos necesarios.

Con el tiempo se agregó la memoria flash a estos sistemas, es decir, las nuevas unidades SSD, lo que hizo que esta memoria disparase el porcentaje de gasto, mientras que AMD y su fuerte reingreso en la competencia por las CPUs para este tipo de sistemas de alto rendimiento hizo que la CPU bajase los costos debido a esta competencia.

Llegados a este punto, tanto la CPU como la memoria principal representaban aproximadamente un tercio del coste total del sistema. Sin embargo, en la actualidad, la memoria RAM suele ser más costosa que el resto de partes, dada la bajada del precio en las unidades SSD y la competencia en cuanto a CPUs para la nube y el HPC.

Cuando hablamos del coste energético, ocurre algo parecido. La CPU sigue siendo uno de los elementos que más consume, seguido de la memoria RAM, y alrededor del 20% para otros periféricos y un 5% para las unidades de almacenamiento flash, que son más eficientes energéticamente que las HDD.

Importancia de la memoria RAM

Además de que la memoria principal o RAM supone un factor de coste importante, y también en el apartado de la energía, hay que agregar que es un factor muy importante. De hecho puede ser un limitante en cuanto al ancho de banda y capacidad, lo que haría del principal cuello de botella para la CPU.

Queremos, por otro lado, que el sistema E/S sea configurable, y eso significa hacer converger los controladores de memoria y los controladores PCIe, o crear un bus o controladores genéricos que pueda comunicarse con la E/S o la memoria RAM. IBM ha hecho un gran avance gracias a la interfaz OpenCAPI que ha integrado en sus procesadores POWER10 por primera vez, pero cuando pensamos en procesadores x86 es otra cosa diferente, y es aquí donde llega el protocolo CXL al rescate…

¿Qué es CXL?

CXL son las siglas de Compute Express Link, es decir, un estándar abierto para conexiones de la CPU a dispositivos y de la CPU a la memoria, consiguiendo una alta velocidad y alta capacidad. Está pensada especialmente para centros de datos de alto rendimiento, aunque veremos si con el tiempo también llega a los PCs.

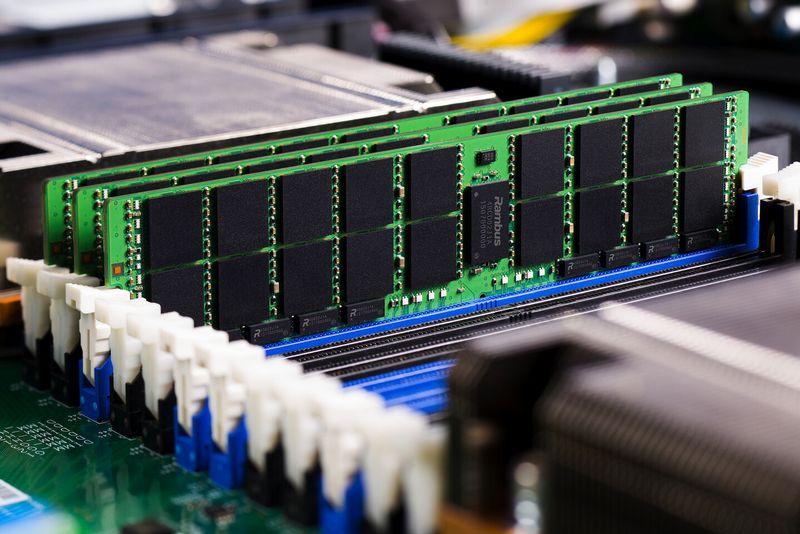

CXL se basa en una interfaz física y eléctrica serial PCIe e incluye un protocolo de E/S de bloque basado en PCIe, además de nuevos protocolos para mantener la coherencia en la memoria caché mientras se accede a la memoria del sistema y la memoria de los dispositivos. De esta forma, se superarían las limitaciones del rendimiento y empaquetado de los módulos DIMM actuales.

El fabricante de chips Marvell, conocido también por sus CPUs para servidores ThunderX basada en ARM, también quiso participar en el juego de la memoria CXL, como otros muchos fabricantes. No obstante, fue Intel la que desarrolló principalmente esta tecnología. Actualmente, el CXL Consortion está formado por multitud de miembros entre los que destaca, Meta, Dell, Cisco, Google, HPE, Huawei, Intel, Microsoft, AMD, NVIDIA, Samsung, ARM, Broadcom, IBM, Ericsson, Qualcomm, Marvell, Microchip Technology, SK Hynix, Western Digital, Rambus, Renesas, Seagate, Micron, Oracle, etc.

En 2020, tanto Gen-Z Consortium y CXL Consortium planearon que ambas tecnologías tuvieran interoperabilidad, apareciendo los primeros resultados en 2021. De esta forma, se desarrollaría un único estándar industrial. Más tarde, en 2022, las especificaciones y los activos de OpenCAPI también se habían transferido al CXL Consortium. Por tanto, ahora se incluyen en el estándar tecnologías como OpenCAPI de IBM, Gen-Z de HPE, CCIX de Xilinx (ahora AMD), InfiniBand/RoCE de Mellanox (ahora NVIDIA), Infinity Fabric de AMD, Omni-Path/QuickPath/UltraPath de Intel y también NVLink/NVSwitch de NVIDIA.

CXL 1.x

En 2019 se lanzó la especificación CXL 1.0 basada en el protocolo PCIe 5.0. Permite a la CPU acceder a la memoria compartida en dispositivos aceleradores con un protocolo coherente para la caché. Más tarde, en ese mismo año, llegaría una mejora de ésta denominada CXL 1.1.

CXL 2.0

En 2020 llegaría la versión CXL 2.0 de esta especificación. Ésta traía una compatibiliad para la conmutación que permitía la conexión de varios dispositivos CXL 1.x y 2.0. Además, también agregaba una implementación para mantener la integridad y el cifrado de datos para seguridad.

CXL 3.0

En 2022 llegaría CXL 3.0 basada en PCIe 6.0, con codificación PAM-4 y con el doble de ancho de banda que sus predecesores. Además, también se agregaban otras mejoras, con coherencia mejorada con DMA punto a punto y uso compartido de memoria.

Implementaciones

Existen varias implementaciones importantes de CXL, como por ejemplo:

- La que Intel anunció en 2019 para su familia Agilex de FPGAs.

- También Samsung anunciaría en 2021 un módulo de expansión basado en DDR5 de 128 GB y más tarde una versión de 512 GB basada en su propio controlador CXL patentado.

- En 2021 llegaría CXL 1.1 para los procesadores Intel Sapphire Rapids (Xeon).

- Lo mismo para los AMD EPYC basados en Zen 4 «Genoa» y «Bergamo».

Protocolos CXL

Si nos adentramos más en el funcionamiento de los protocolos de CXL, este estándar se define sobre tres protocolos separados que debes conocer:

- CXL.io: se basa en PCIe 5.0 con mejoras y proporciona configuración, inicialización y administración de enlaces, así como descubrimiento y enumeración de dispositivos, interrupciones, DMA y registro de acceso a E/S mediante Load/Store no coherentes.

- CXL.cache: permite que los dispositivos periféricos conectados al E/S puedan acceder de manera coherente a la memoria caché de la CPU con una interfaz de baja latencia.

- CXL.mem: permite que la CPU pueda acceder de forma coherente a la memoria del dispositivo en caché con comandos Load/Store para el almacenamiento volátil (RAM) y no volátiles o persistente (flash).

Retos a los que se enfrenta los sistemas de memoria

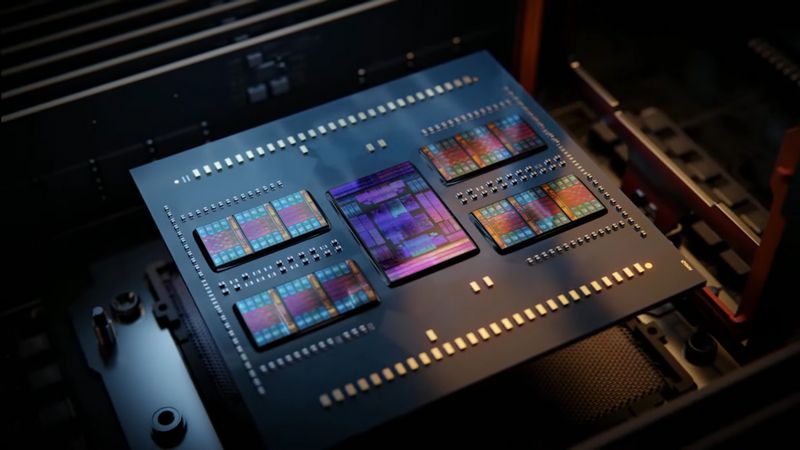

Como bien sabes, la memoria debe conectarse a una CPU, GPU, DPU, y otras unidades, mediante un controlador de memoria. Esto genera dos problemas, por un lado se tiene una memoria costosa que se termina infrautilizando, y problemas para escalar estos sistemas de alto rendimiento. Por tanto, hay que buscar una solución para una memoria más compartible y escalable.

También hay que tener en cuenta que el número de núcleos de la CPU se está disparando de forma más rápida que el aumento del ancho de banda de la memoria principal, lo que abre una brecha de rendimiento entre los núcleos y los módulos DIMM que los alimentan, generando un cuello de botella para la CPU.

Con CXL y todos estos proyectos, lo que se busca es precisamente tener sistemas de memoria convergente y que puedan superar estos inconvenientes. De hecho, ya se mira a CXL como el estándar que todos seguirán a largo plazo. Poco a poco está ganando mucha tracción en el sector, y seguirá así.

Empresas que han surgido en torno a esta tecnología, podrán ayudar a crear factores de forma DIMM estándar, pero con controladores de expansión CXL, además de módulos de memoria más anchos y altos de factores de forma superiores a DIMM para albergar más capacidad en un solo slot.

CXL abrirá el ancho de banda para la memoria sobre los controladores DRAM y PCIe en los procesadores modernos. Por ejemplo, en la actualidad, si quieres expandir el ancho de banda, puedes agregar un módulo DIMM a cada canal de memoria, pero luego cada DIMM obtiene la mitad del ancho de banda de la memoria.

En cambio, con el controlador CXL, al agregar módulos DIMM se usarán carriles PCIe para agregar un ancho de banda superior, aunque bien es cierto que la latencia no es tan baja en PCIe en comparación con los controladores DRAM/HBM, funciona bastante bien. Y con la llegada de PCIe 6.0, esto mejorará para las futuras DDR5 y DDR6.

El futuro

Además, de cara al futuro, CXL es muy prometedor, ya que esta expansión es solo la primera etapa de la evolución. No se tardará demasiado en que los chips controladores CXL también se empleen en otros tipos de procesadores que a menudo son incompatibles. Incluso podremos ver que se puede crear un tejido entre los dispositivos de memoria y las diferentes unidades de cómputo.

En la visión de Marvell, una de las desarrolladoras de chips controladores CXL, habrá una memoria que podrá conectar lo que ella llama unidades XPU (CPU, APU, GPU, DPU, TPU,…). De esa forma, se ayudará a resolver los problemas actuales y a que los sistemas que necesitan hiperescalabilidad puedan escala.

No obstante, aún quedan algunos años para conseguir una buena compatibilidad dentro de los sistemas para centros de datos y HPC. Y quién sabe si también llegará en algún momento a los PCs, para agregar mejoras notables en el rendimiento.

¿Tú qué opinas? No olvides comentar…