El endurecimiento contra radiación, o radiation hardened, es una práctica destinada a proteger la electrónica, como los chips semiconductores, de los daños causados por la radiación ionizante. Algo muy importante para algunas aplicaciones militares, espaciales, o para uso en la industria nuclear. ¿Quieres saber cómo se protegen? Aquí te lo explicamos…

Índice de contenidos

Fuentes de radiación

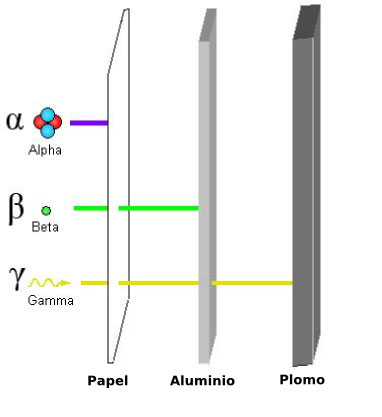

La radiación ionizante es un problema para muchos circuitos integrados y otros dispositivos electrónicos, ya que pueden sufrir daños a consecuencia de la radiación beta y gamma especialmente. Los daños pueden ser puntuales en algunos casos, y llegar a la destrucción total en otros.

Las fuentes de radiación pueden venir de muchos sitios, no solo de lo nuclear. Por ejemplo:

- Eventos de partículas solares (SPE): provenientes del sol, y con protones de alta energía e iones pesados con rayos X.

- Radiación de Van Allen: son cinturones alrededor de la Tierra que atrapan partículas como electrones y protones de alta energía debido a la magnetosfera.

- Rayos cósmicos (GCR): provienen del espacio y están compuestos por protones en un 85%, partículas alfa en un 14%, e iones pesados con radiación X en un 1%.

- Partículas secundarias: son las que provienen de reactores nucleares, desechos nucleares, explosiones nucleares o termonucleares (estas también producen EMP), etc., y suelen ser radiación gamma y neutrones. Incluso los empaquetados de los propios chips pueden contener isótopos radiactivos que pueden afectar.

Problemas producidos por la radiación

La radiación citada anteriormente puede generar varios tipos de daños causados principalmente en la red cristalina de los semiconductores, desplazando algunos de los átomos y alterando las propiedades eléctricas a causa de impactos de neutrones, protones, partículas alfa, iones pesados, y fotones gamma de alta energía. También puede traer efectos de ionización en las capas de óxido de puerta en los FETs cuando las dosis de radiación son altas o por exposición prolongada a partículas cargadas, aunque no sean de alta energía.

Se puede decir que los efectos se catalogan en

- Efectos de dosis ionizante total: la exposición prolongada a la radiación ionizante puede causar daños en la estructura cristalina del semiconductor. En los chips CMOS, esto puede generar la formación de pares de agujeros y electrones recombinados en las capas aislantes de la puerta del transistor. Esto resulta en una polarización persistente en la puerta y afecta el voltaje umbral, lo que dificulta la conmutación de los transistores de canal P al estado activo y facilita la conmutación de los transistores de canal N. En casos extremos, esto puede llevar a que los transistores queden permanentemente apagados o encendidos.

- Efectos de dosis transitoria: estos efectos ocurren cuando el semiconductor es expuesto a un pulso de radiación de alta intensidad pero de corta duración, como en una explosión nuclear. Esto genera fotocorrientes en todo el cuerpo o sustrato semiconductor, lo que puede causar activaciones aleatorias de los transistores y generar estados lógicos incorrectos en flip-flops y celdas de memoria, en particular. Si el pulso es lo suficientemente fuerte, puede provocar daños severos en las uniones.

- Efectos de evento único (SEE): estos efectos afectan principalmente a los chips digitales y han sido estudiados más recientemente. Cuando una partícula de alta energía atraviesa el semiconductor, deja un rastro ionizado que puede generar efectos similares a los de la dosis transitoria. Estos eventos pueden clasificarse en seis categorías diferentes:

- Trastornos de evento único (SEU): son cambios en el estado de los bits de memoria causados por un solo ion. Algunos dispositivos son especialmente sensibles, y un SEU puede perturbar múltiples celdas de memoria adyacentes, alterando varios estados de bits.

- Latchup de evento único (SEL): cuando un ión pesado o un protón de alta energía pasa a través de dos uniones de un transistor, generando un efecto similar a un tiristor y dejándolo permanentemente en cortocircuito hasta que el equipo se apague y reinicie.

- Transitorio de evento único (SET): ocurre cuando una carga recolectada de un evento de ionización se descarga como una señal que viaja por el circuito, generando un efecto similar a una descarga electrostática (ESD).

- Snapback de evento único: similar al SEL, pero no requiere una estructura PNPN para ocurrir. Puede ocurrir en transistores MOS de canal N cuando un ión golpea cerca de la unión del drenaje, generando una avalancha de

- Efectos EMP: estos efectos son causados por el destello de radiación que atraviesa los equipos, lo que resulta en la ionización local de algunas áreas y corrientes eléctricas en el material.

- Efectos de neutrones: pueden interactuar con la estructura cristalina de los semiconductores, desplazando átomos y causando perturbaciones en los portadores minoritarios, generando problemas como ruido y eventos individuales. Este impacto es más notable en dispositivos bipolares en comparación con los CMOS. Los LEDs de GaAs son particularmente sensibles a los neutrones.

Técnicas Radiation hardened (RD)

Para proteger los chips, se pueden aplicar varias técnicas que se pueden subdividir en:

Radiation Hardened físico

Son técnicas que se implementan a nivel físico, es decir, durante la fabricación del chip para que éste resulte inmune o menos vulnerable a la radiación:

SOI y SOS: sustratos aislantes vs bulk

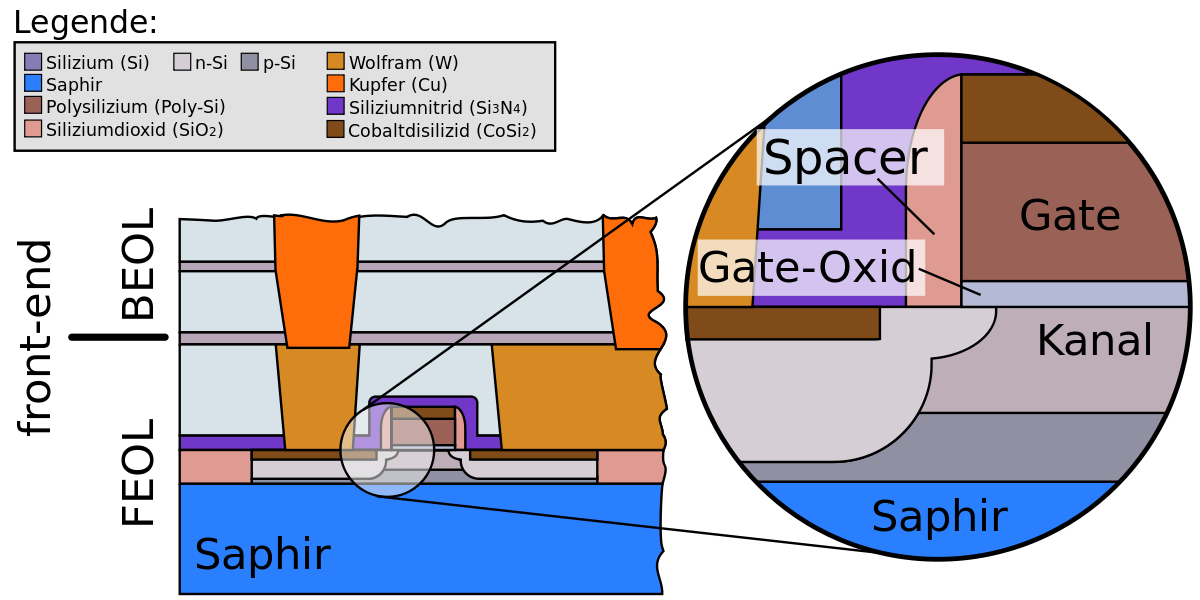

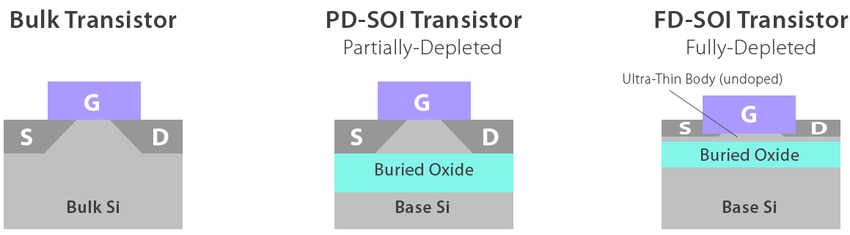

Las técnicas de protección contra la radiación, como el uso de sustratos aislantes en las obleas, como SOI (Silicon On Insulator) y SOS (Silicon on Sapphire), han sido empleadas por AMD e IBM durante varios años.

Estas tecnologías ofrecen beneficios como la reducción de la capacitancia parásita y una mayor resistencia al enganche o acoplamiento debido al aislamiento en los pozos N y P. El SOS, que utiliza zafiro como aislante, proporciona mejoras en el rendimiento, aunque es más costoso y se utiliza principalmente en aplicaciones espaciales y militares. Por otro lado, los chips SOI se utilizan más en aplicaciones comerciales. En términos de tolerancia a la radiación, los chips SOI y SOS de grado espacial pueden soportar dosis mucho más altas en comparación con los chips comerciales estándar.

Super Junction

Los circuitos integrados bipolares utilizan transistores de unión bipolar (BJT) como componentes principales. Estos dispositivos electrónicos de tres terminales se utilizan para amplificación y conmutación, y su funcionamiento implica tanto electrones como huecos. La corriente fluye en un BJT a través de la difusión bidireccional de portadores de carga entre dos regiones con diferentes concentraciones de carga. A diferencia de los transistores unipolares, como los MOSFET, que involucran un solo tipo de portador de carga en la corriente debido a la deriva.

En el campo de la electrónica de potencia, ha surgido un nuevo concepto llamado Super Junction (SJ) para desarrollar interruptores de alta potencia con conmutación de baja pérdida. El transistor bipolar de superunión (SJBT) comparte similitudes con el MOSFET de superunión y se utiliza en aplicaciones de conversión de energía y electrónica de potencia.

Además, el transistor de alta movilidad de electrones pseudomórfico (PHEMT) de GaAs ha experimentado un desarrollo significativo y se utiliza en aplicaciones de alta frecuencia, como comunicaciones digitales y redes celulares. Este dispositivo ofrece excelentes propiedades de reducción de ruido y es adecuado para aplicaciones de alto rendimiento.

Celda SRAM tolerante a radiación

Para aumentar la resistencia a la radiación, se reemplaza la tecnología de DRAM por una SRAM más resistente, aunque más grande y costosa. Una forma de mejorar la resistencia de una SRAM utilizada principalmente en estado de lectura es agregar una resistencia de alto valor. Esto protege la SRAM contra los efectos de la radiación en niveles altos. En aplicaciones donde la SRAM se programa solo una vez durante el encendido y no se modifica posteriormente, este enfoque es especialmente útil.

Se han realizado estudios para abordar los desafíos en el diseño de celdas SRAM en tecnología SOI parcialmente agotada (PD-SOI). Estos estudios analizan los efectos del potencial de cuerpo flotante y el comportamiento bipolar parásito, así como las características de endurecimiento contra alteraciones de un solo evento (SEU) y endurecimiento contra la radiación de dosis total de las SRAM SOI.

WBG

La utilización de sustratos de brecha ancha (WBG o Wide Band-Gap Sustrate) mejora la tolerancia a defectos en dispositivos electrónicos. Los materiales WBG, como el nitruro de galio (GaN) y el carburo de silicio (SiC), son considerados prometedores para futuros componentes electrónicos debido a su capacidad de potencia, resistencia a la radiación, alta temperatura de operación y otras ventajas. Sin embargo, se necesita más investigación y desarrollo para mejorar la calidad de los materiales, fabricar dispositivos más eficientes y confiables, comprender mejor la física de los semiconductores y desarrollar técnicas avanzadas de empaquetado. Además, es importante evaluar detalladamente las aplicaciones para aprovechar al máximo los beneficios de estos materiales en sistemas espaciales.

Encapsulado blindado

Recientemente, se ha investigado el uso del suelo lunar como escudo contra la radiación espacial. Estudios han demostrado que incluso una cantidad moderada de suelo lunar proporciona una protección significativa contra la radiación cósmica galáctica y los eventos de partículas solares, dejando solo una dosis residual moderada de rayos pesados.

Un estudio comparó el uso de aluminio (baja/mediana Z) y tungsteno (alta Z) en la protección de naves espaciales y encontró que el material de alta Z es más eficiente en términos de masa y área para la atenuación de radiación en entornos específicos como Júpiter. Sin embargo, la combinación de materiales de baja/alta Z es más efectiva en términos de masa y área cuando se requiere un blindaje masivo para proteger componentes electrónicos extremadamente sensibles a la radiación.

Boro empobrecido como blindaje

El boro empobrecido, compuesto por el isótopo boro-11, se utiliza en semiconductores para proteger contra los efectos dañinos de la radiación espacial. Cuando la radiación cósmica golpea las estructuras de las naves espaciales, se generan neutrones secundarios que pueden causar fisión en el boro-10 presente en los semiconductores. Esto resulta en la emisión de rayos gamma, partículas alfa e iones de litio, lo que puede llevar a la pérdida de datos o alteraciones en los bits.

Sin embargo, el uso de boro empobrecido, enriquecido en boro-11, previene la fisión del boro-10 y protege los chips de las descargas de carga y la pérdida de datos, ya que el boro-11 es inmune al daño causado por la radiación. Esta medida de contramedida contribuye a reducir los efectos perjudiciales de la radiación espacial en los semiconductores.

Self-Healing

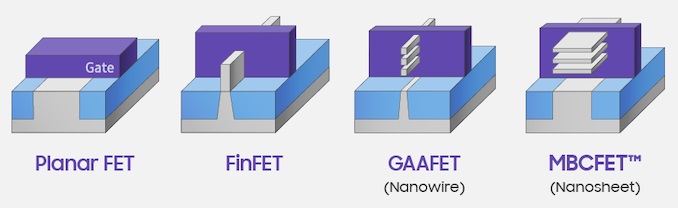

Se ha desarrollado un enfoque de auto-reparación en circuitos conscientes ante la radiación utilizando transistores de nanohilos «Gate-All-Around» (GAA). Mediante el calentamiento controlado a más de 900 °C en menos de 10 nanosegundos, se demostró que se puede reparar la degradación del rendimiento causada por la radiación, el estrés y la edad. Este sistema se probó en componentes críticos de una nave espacial, como un microprocesador, memoria DRAM y unidad de memoria flash. Se logró prolongar la vida útil de los dispositivos y tratar repetidamente los defectos causados por la radiación. La tecnología ofrece resistencia a los rayos cósmicos y la posibilidad de utilizar circuitos más pequeños, abriendo oportunidades para viajes espaciales de larga distancia con nano-naves sostenibles.

Más alternativas

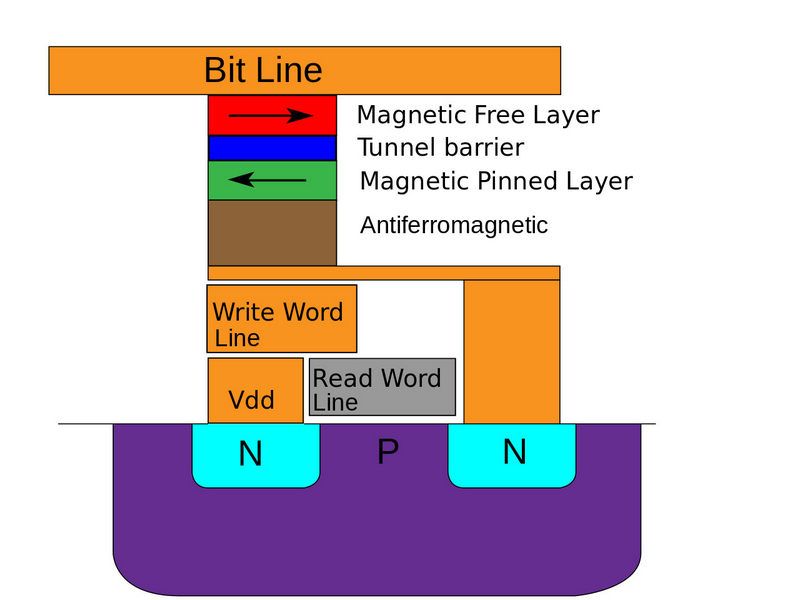

Además de los enfoques previamente mencionados, existen otras estrategias para proteger físicamente los dispositivos electrónicos. Por ejemplo, se puede utilizar la tecnología MRAM (Magnetoresistive RAM) en lugar de la SDRAM convencional para endurecer los dispositivos, ya que la MRAM no es vulnerable a los problemas causados por la ionización.

Otra forma de mejorar la resistencia a la radiación es mediante el uso de nodos o procesos de fabricación especiales, conocidos como RHBP (Rad-Hard By Process), como los nodos de 150 nm de 2016 o 65 nm, entre otros.

En relación a las celdas SRAM en lugar de la DRAM, es importante destacar que la SRAM tampoco es completamente inmune a la radiación. Para mejorar su fiabilidad ante la radiación, se pueden utilizar celdas con más transistores que las convencionales (4T o 6T), lo que las hace más tolerantes a eventos SEU (Single Event Upset). Sin embargo, esto implica una menor densidad de memoria por unidad de superficie, menor eficiencia energética y un mayor coste.

También existe una técnica llamada «Edge-less CMOS», que utiliza transistores con una construcción física y un diseño de layout poco convencionales.

Otra forma de actuar es mediante la redundancia de equipos, como tienen muchas aeronaves, satélites, rovers, etc. Es decir, en vez de emplear un solo sistema electrónico, tienen varias réplicas por si uno de ellos falla.

Radiation hardened lógico

Por otro lado, también se pueden implementar medidas de endurecimiento contra radiación (radiation hardened) de forma lógica. Generalmente, estas medidas suelen usarse como complemento de las anteriores, y tenemos ejemplos como:

Corrección de errores

La memoria de detección y corrección de errores, conocida como ECC o EDAC, ofrece protección contra errores en la memoria DRAM mediante el uso de códigos de corrección de errores. Es especialmente útil en aplicaciones que requieren alta tolerancia a fallos, como servidores y entornos espaciales afectados por radiación cósmica. Esta memoria utiliza bits de paridad adicionales para verificar y, en algunos casos, corregir datos corruptos. Un circuito llamado depurador escanea continuamente la memoria para detectar posibles errores causados por la radiación.

El proceso de corrección de errores implica leer los datos, verificar la paridad para detectar errores y corregirlos en caso de que se detecten en la RAM. Los controladores de memoria con corrección de errores utilizan principalmente códigos Hamming, aunque algunos pueden emplear redundancia modular triple (TMD). La técnica de interleaving distribuye el efecto de un rayo cósmico en varios bits vecinos a través de múltiples palabras de memoria, asignando bits vecinos a diferentes palabras. Esto permite corregir alteraciones causadas por eventos únicos (SEU) siempre que no superen el umbral de error en una palabra específica entre accesos, lo que garantiza un sistema de memoria aparentemente libre de errores.

También te puede interesar comprar las mejores memorias RAM del mercado

Corrección por software

Por supuesto, también se puede implementar mediante software la corrección o comprobación de posibles errores, además de otras técnicas como la temporización de vigilancia, es decir, disponer de un temporizador de vigilancia que realice un reinicio completo del sistema si no se realiza una secuencia específica. También se pueden usar diversas máquinas virtuales ejecutándose en paralelo como modo de redundancia lógica, con un hypervisor especialmente diseñado para una alta confiabilidad….

Ejemplos de chips radiation hardened

Para finalizar, vamos a ver algunos ejemplos de los más importantes de chips protegidos contra radiación, como:

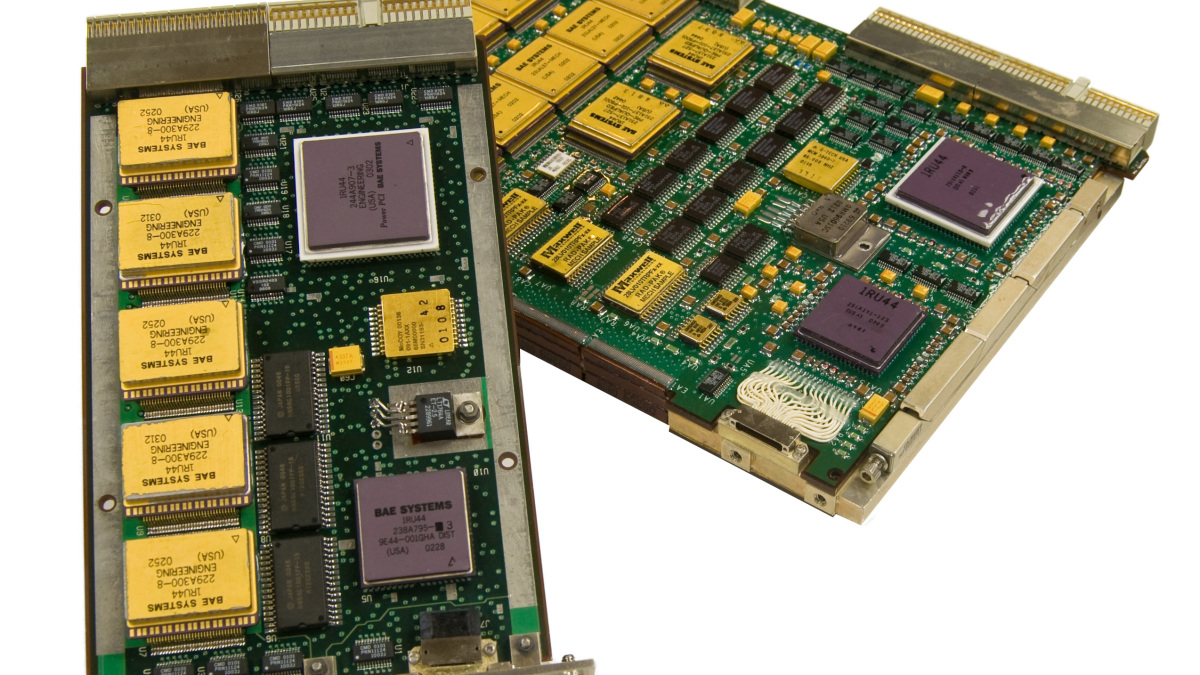

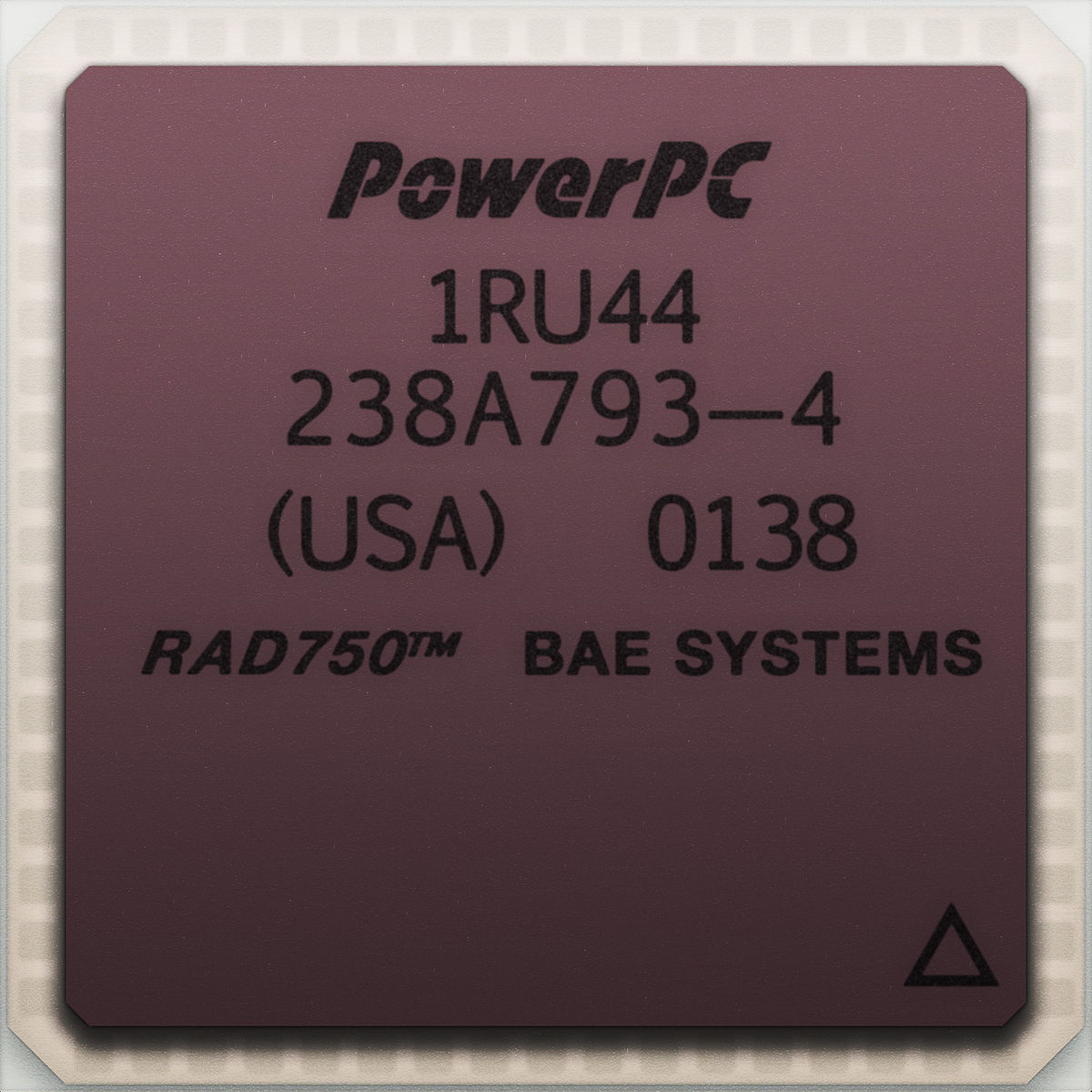

- BAE System creó uno de los chips más populares, el RAD-750. Se trata de un PowerPC 750 de IBM con técnicas radiation hardened para su uso en el espacio.

- En Europa, la ESA también tiene sus propios chips LEON 2, LEON 3, LEON 4 y LEON 5. Estos chips han sido desarrollados por Gaisler Research, y son de código abierto. Se producen en la empresa sueca Cobham Semiconductor Solution.

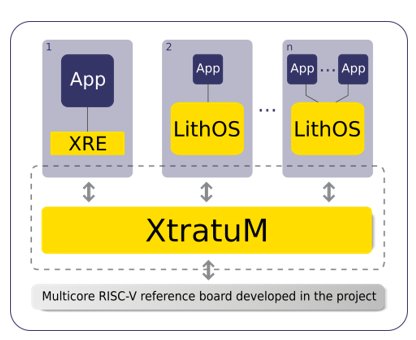

- Cobham Gaisler también ha sustituido la ISA SPARC de los LEON por la RISC-V en su proyecot NOEL-V más actual, para misiones de la ESA, junto con el software de la española De-RISC Project.

- ARM también tiene chips endurecidos, como el HPSC basado en Cortex-A53 usado por la NASA y la United States Air Force.

- Y otros muchos…

A esta lista habría que agregar otros muchos casos, aunque estos son los más importantes.