Como sabes, cada CPU habla su propio «idioma», y ese idioma son las instrucciones de la ISA a la que entiende. Sin embargo, muchos se pueden estar preguntando si se podría crear un microprocesador que hablase distintas «lenguas», para así poder ejecutar binarios de plataformas diferentes en un mismo equipo. Pues aquí va la respuesta:

Índice de contenidos

¿Qué es la ISA de un microprocesador?

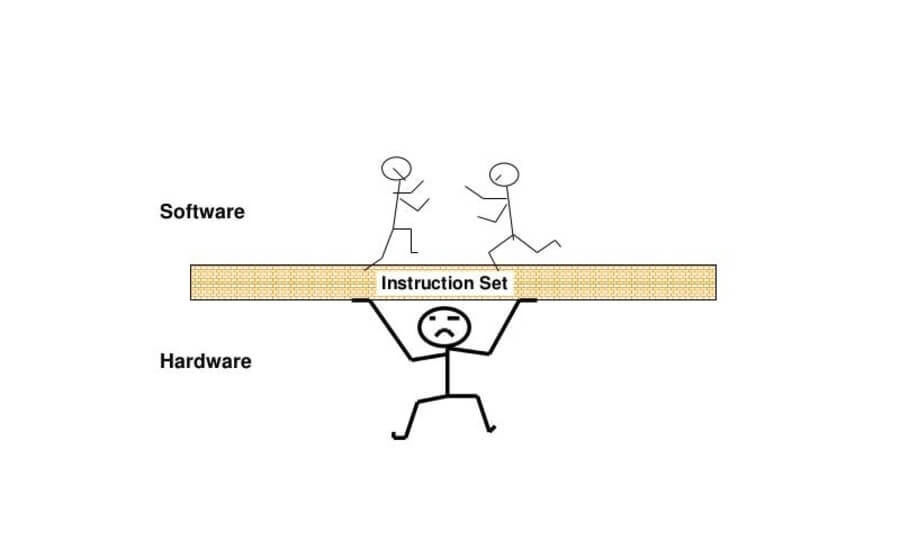

Una arquitectura de conjunto de instrucciones, también conocida como Instruction Set Architecture (ISA), es un conjunto de instrucciones que define las operaciones que una Unidad Central de Procesamiento (CPU) puede realizar, así como los tipos de datos que puede manipular, los modos de direccionamiento, los registros y la longitud de palabra.

La ISA desempeña un papel fundamental al establecer la interfaz entre el hardware y el software de un sistema informático. El software, incluyendo el sistema operativo y las aplicaciones, se desarrolla en un lenguaje de programación de alto nivel como C o Java, el cual se compila en un conjunto de instrucciones de bajo nivel específicas de una ISA determinada. A su vez, la CPU está diseñada para ejecutar eficientemente y de manera rápida estas instrucciones, decodificándolas en la unidad de control, como he mencionado anteriormente.

Es decir, en definitiva se podría entender como el lenguaje que entiende la CPU, aunque realmente los mnemónicos de las instrucciones se manejan a nivel lógico como unos y ceros. Pero, lo que trato de que entiendas es que a pesar de que todos los microprocesadores se basan en código máquina binario, no todos entienden las mismas instrucciones. Es decir, aunque todas las lenguas del mundo usen palabras para construir el lenguaje, no todos comprendemos todos los lenguajes, ¿verdad?

Algunos ejemplos de ISA los tenemos en la x86-64, ARM, MIPS, RISC-V, SPARC, POWER, z/Architecture, etc.

También te puede interesar conocer los mejores procesadores del mercado basados en x86-64

La implementación de una ISA en un procesador específico, ya sea una CPU, una GPU u otro tipo de procesador, se conoce como microarquitectura. La microarquitectura se refiere a cómo los diseñadores de procesadores organizan los componentes internos del procesador para ejecutar las instrucciones definidas por la ISA. La microarquitectura se centra en los aspectos detallados a nivel de circuito del procesador, que incluyen la organización de los registros internos, la unidad de control, las unidades de ejecución, las cachés, el sistema de interconexión y otros elementos. El diseño de la microarquitectura debe asegurar que las instrucciones se ejecuten de manera eficiente, rápida y con un consumo de energía mínimo.

¿Puede un microprocesador usar varias ISAs?

Sí, es factible que existan múltiples microarquitecturas distintas para una misma ISA. La ISA representa la especificación de un conjunto de instrucciones que un procesador debe ser capaz de interpretar y ejecutar, como se mencionó previamente. Por otro lado, la microarquitectura se refiere a la implementación específica de esa ISA en un procesador. Por lo tanto, aunque dos procesadores puedan compartir la misma ISA, es posible que posean microarquitecturas diferentes.

Esto implica que presenten distintos diseños internos de hardware, organización de unidades funcionales, tipos y tamaños de caché, y otros factores. Un ejemplo de esto es la diferencia entre un Intel Core y un AMD Ryzen, ambos utilizando la misma ISA x86-64 pero con microarquitecturas distintas. Esto también se aplica a procesadores como el AMD Zen 3 y Zen 4, o el Intel Meteor Lake y Raptor Lake, donde se emplean diferentes microarquitecturas pero se comparte la misma ISA.

La elección de una microarquitectura específica para implementar una ISA depende de diversos factores, como el rendimiento deseado, la eficiencia energética, el costo y el tiempo de desarrollo. Por ejemplo, una microarquitectura que priorice el rendimiento puede incorporar una mayor cantidad de unidades de ejecución y cachés de mayor tamaño. Por otro lado, una microarquitectura orientada a la eficiencia energética puede contar con menos unidades de ejecución y cachés de menor tamaño.

En los procesadores heterogéneos actuales, es común encontrar diferentes microarquitecturas en los diversos núcleos. Por ejemplo, el Intel Core i9-13900K Raptor Lake-S está compuesto por P-Cores y E-Cores, donde los núcleos de alto rendimiento se basan en la microarquitectura Raptor Cove, mientras que los núcleos de alta eficiencia se basan en la microarquitectura Gracemont. Ambos comparten la misma ISA, pero pueden admitir extensiones diferentes.

MISA (Multiple Instruction Sets Architecture): una misma microarquitectura y diferentes ISAs

Un núcleo Composite-ISA es una forma de diseño de procesador que combina múltiples conjuntos de instrucciones, o ISAs, en una única unidad de procesamiento. La finalidad de un núcleo Composite-ISA es brindar mayor flexibilidad y eficiencia en la ejecución de diversas aplicaciones y tareas, sin tener que recurrir a la emulación de software o capas que puedan afectar el rendimiento.

A este enfoque también se le conoce como MISA (Multiple Instruction Set Architecture). En resumen, un procesador MISA tiene la capacidad de cambiar entre diferentes ISAs para adaptarse a distintos tipos de aplicaciones o tareas. La idea detrás de MISA radica en que diferentes aplicaciones poseen requisitos de procesamiento distintos y, por lo tanto, pueden beneficiarse de conjuntos de instrucciones diferentes.

Aunque los procesadores con arquitecturas MISA son poco comunes y han sido escasos a lo largo de la historia, esto no significa que sean imposibles. La implementación de MISA puede adoptar diversas formas. Una opción es contar con múltiples núcleos o procesadores, cada uno de ellos con su propio conjunto de instrucciones especializado.

Otra opción es tener un solo procesador con múltiples unidades de ejecución y conjuntos de instrucciones diferentes, diseñados para manejar tareas específicas. Estas configuraciones pueden ser prácticas en situaciones en las que ciertas CPUs necesitan ser compatibles con software compilado para otra ISA, pero no tienen la licencia para utilizar esa ISA específica. Esto se ha observado en algunos chips desarrollados por China o Rusia, donde se busca evitar la dependencia de tecnología estadounidense.

¿Por qué no se hace para mejorar la compatibilidad del software?

Cuanto más diferentes sean las ISAs, más desafiante se vuelve el proceso. También implica mayores costos generales, especialmente en algunas partes específicas de la microarquitectura. No es simplemente cuestión de añadir un front-end diferente a un diseño de microarquitectura de back-end común. Si solo se tratara de un costo adicional en términos de área para los decodificadores diferentes, sin afectar la potencia o el rendimiento, sería algo menor y factible en la actualidad, dada la disponibilidad de transistores en grandes cantidades. Además, debemos considerar que no solo se requiere trabajo en el hardware, sino también en el software, especialmente en el sistema operativo, que debe ser compatible con las diversas ISAs empleadas y funcionar adecuadamente con los diferentes binarios que se deben gestionar.

Agregar capacidad de compatibilidad con ARM a un procesador x86, por ejemplo, ralentizaría el rendimiento y reduciría la eficiencia en el consumo de energía cuando se ejecuta código x86-64 puro. Además, requeriría más área en el chip debido a la necesidad de crear un front-end más complejo para manejar ambas instrucciones. Comercialmente, esto no sería viable debido al mercado limitado y la necesidad de un sistema operativo especial o software de hipervisor para aprovecharlo. Ejecutar instrucciones de la ISA ARM requiere una microarquitectura especialmente optimizada para lograr rendimiento y eficiencia, lo mismo ocurre con x86. Sin embargo, desarrollar un procesador de alto rendimiento y eficiencia que admita varias ISAs es un desafío considerable.

Además, incluso el back-end, es decir, las unidades de ejecución, tendrían que ser modificadas, ya que una ISA podría requerir ciertas operaciones que otra no necesite. Por ejemplo, en el caso de las SIMD de ARM, existen instrucciones que pueden generar hasta 2 salidas de datos, mientras que en las SIMD de x86 solo generan una salida de datos. Esto también afectaría la forma en que se implementan los registros, los puertos necesarios, entre otros aspectos. Además, en el caso de x86 y ARM, estamos hablando de una arquitectura CISC y RISC respectivamente, y aunque los procesadores x86 actuales funcionan de manera similar a RISC a nivel de hardware, no son RISC puros y tienen diferencias arquitectónicas.

En el caso de mezclar binarios de diferentes ISAs, también surgen otros problemas. Cualquier forma de paralelismo, por mínimo que sea, implicaría cambios de contexto más complejos que cuando se utiliza una sola ISA, para evitar la mezcla de flujos de instrucciones diferentes y prevenir errores. Esto, además de ser complicado, puede resultar en una menor velocidad de ejecución. Las diferencias también se pueden observar en los movimientos de datos, los modos de direccionamiento y las tablas de páginas de memoria, entre otros aspectos, lo que afecta tanto a la CPU como al sistema operativo. Por ejemplo, el kernel del sistema operativo debería identificar si se está ejecutando una ISA u otra, para realizar las llamadas al sistema o syscalls correspondientes, ya que no serían iguales en ambos casos.

Por este motivo, en la mayoría de los casos lo mejor es evitar este tipo de problemas y de complejidad a nivel de hardware e ir directamente a por soluciones basadas en software, como la emulación para poder ofrecer estas traducciones de binarios o sistemas diferentes en una misma máquina. Algunos ejemplos de ello son QEMU (es modular y admite multitud de arquitecturas diferentes), Rosetta (traduce de PowerPC a x86-64) y Rosetta 2 (traduce de x86-64 a ARM) de Apple, etc.

Ejemplos históricos

Para finalizar, comentaré sobre algunos ejemplos de procesadores que han usado varias ISAs a lo largo de la historia, y que quizás no conocías:

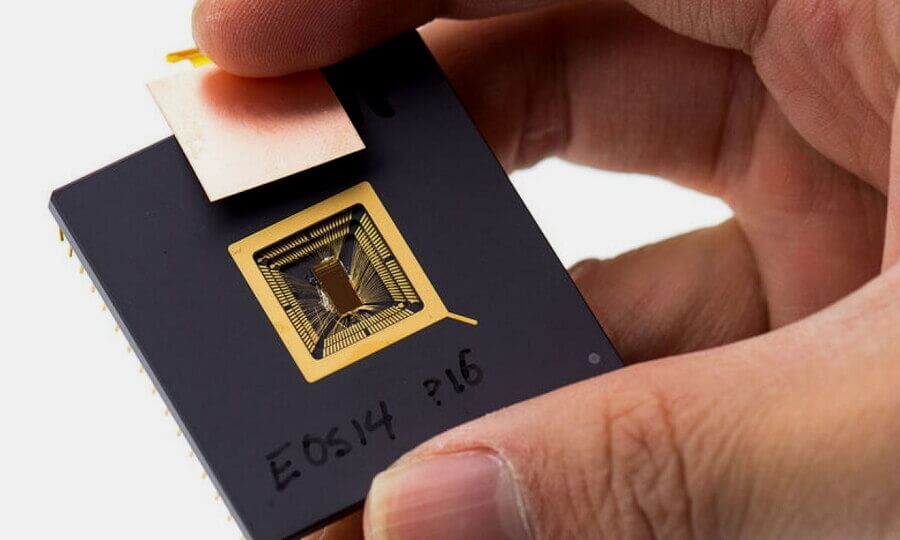

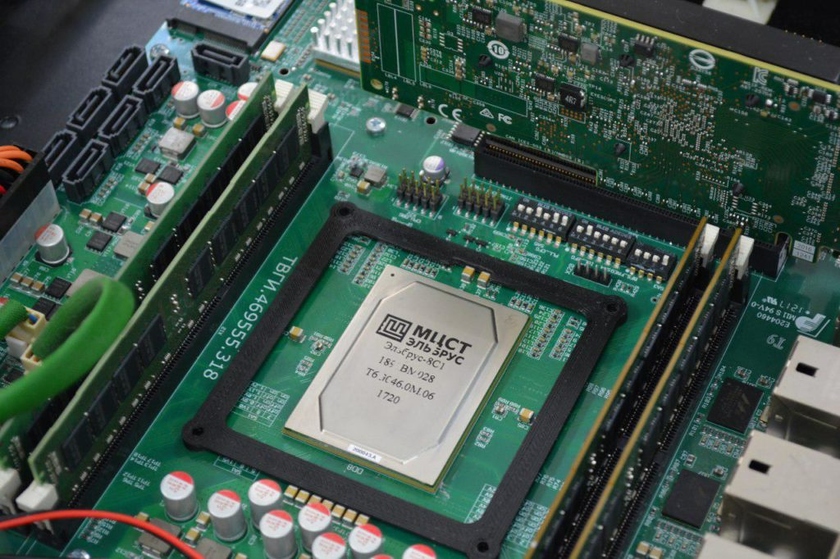

Elbrus

Este chip es creado por la compañía MCST de Rusia y emplea una arquitectura de conjunto de instrucciones llamada Elbrus. Además, posee compatibilidad con la ISA x86 de Intel, lo que le permite ejecutar software diseñado para x86 en Windows y Linux. Inicialmente, estos procesadores también utilizaban la ISA SPARC, aunque han desarrollado su propia arquitectura en la actualidad.

IBM PowerPC 615

IBM desarrolló este procesador para su uso en servidores y estaciones de trabajo. Está basado en la arquitectura PowerPC y también ofrece compatibilidad con la ISA x86 mediante la implementación de un núcleo x86. Este procesador es capaz de funcionar con el sistema operativo en modo 32 bits o 64 bits, tanto en entornos PPC, como en el modo x86-32 e incluso en un modo mixto que combina los tres, aunque el cambio de contexto en el modo mixto puede generar cierto retraso. Los únicos sistemas operativos que brindaron soporte para este chip fueron una versión especial de IBM de OS/2 y Minix.

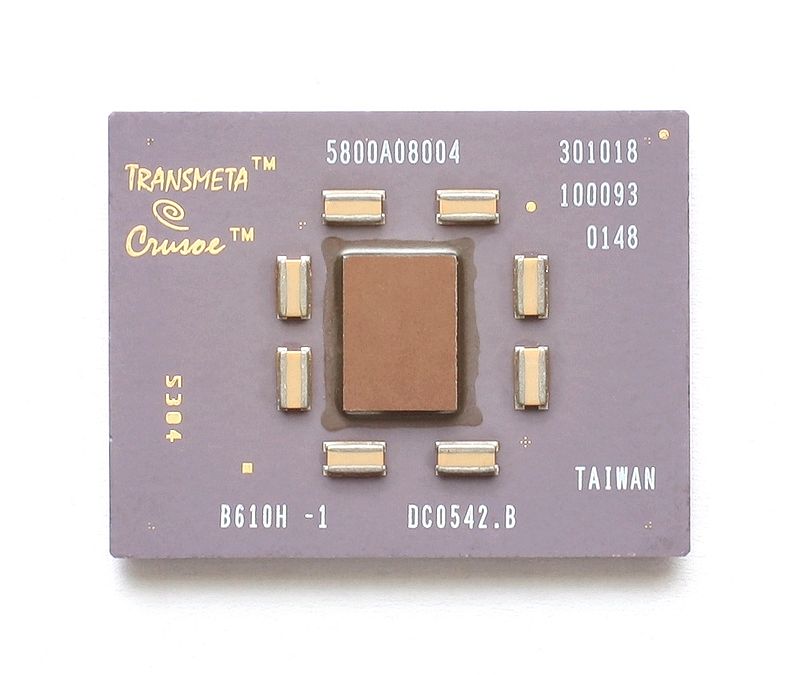

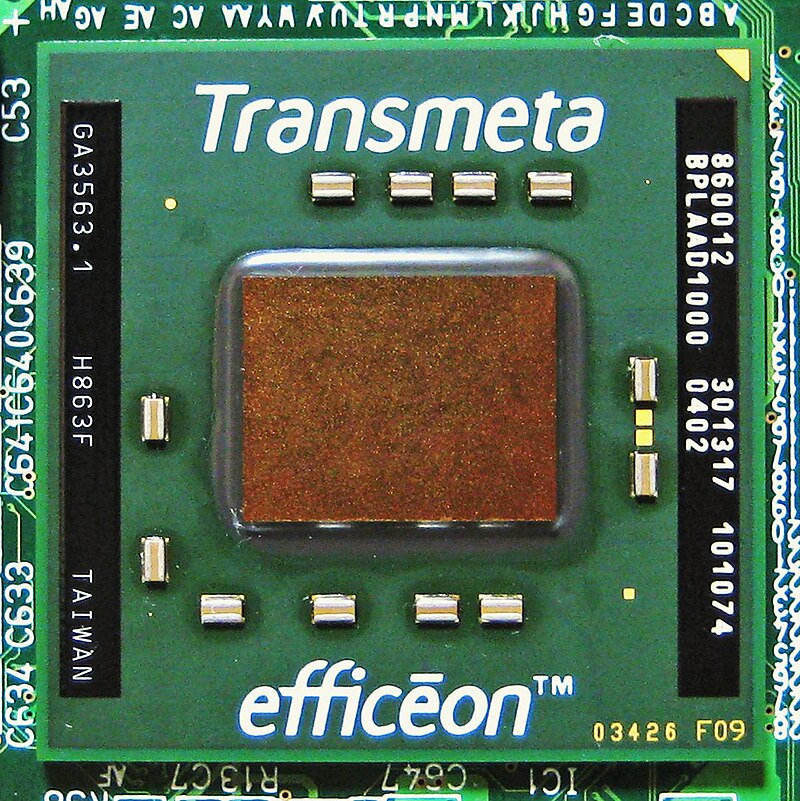

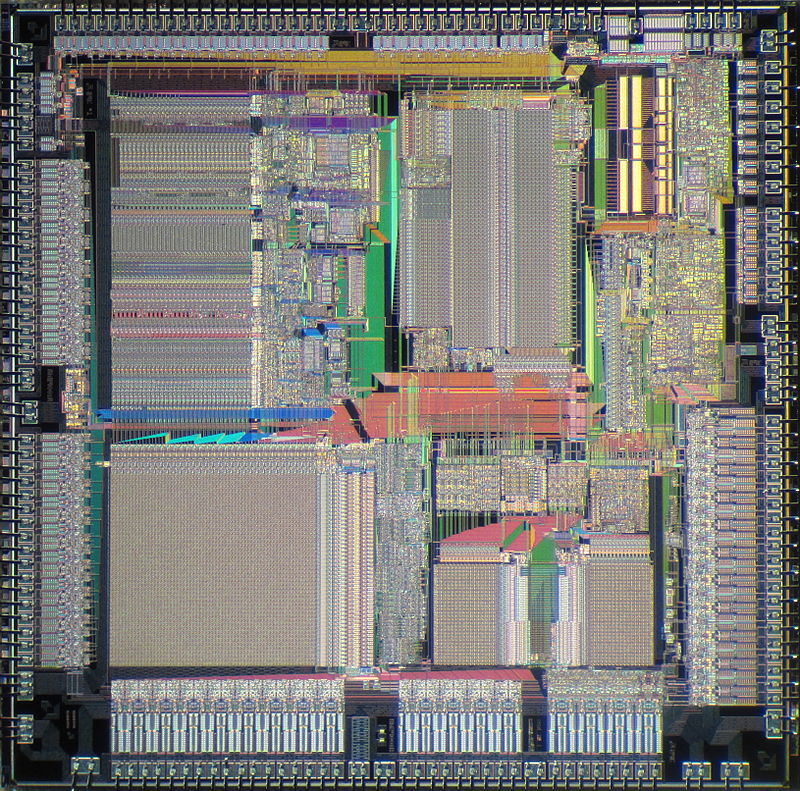

Transmeta Crusoe y Efficeon

El procesador tenía compatibilidad con las arquitecturas ISA x86 y VLIW (Very Long Instruction Word). La capacidad de ser compatible con VLIW permitió al procesador ejecutar instrucciones complejas de manera más eficiente, lo que se tradujo en un mayor rendimiento y menor consumo de energía. Esto fue posible gracias a un método conocido como Code Morphing, desarrollado por Linus Torvalds mientras trabajaba en esta empresa. El Code Morphing permitió que el procesador fuera compatible con software diseñado para x86, a pesar de que su arquitectura de hardware se basaba en VLIW.

Traducción por hardware: o cómo traducir CISC en RISC-like

Tanto Intel con su Pentium Pro como AMD con su K5 adoptaron enfoques similares para mantener la compatibilidad con el software diseñado para la arquitectura CISC x86, al mismo tiempo que aprovechaban las ventajas de una arquitectura RISC a nivel de hardware. Un dato interesante es que AMD utilizó como base el procesador AMD 29000, que era un chip RISC ampliamente reconocido en ese tiempo, y agregó un traductor de instrucciones CISC a RISC-like en el front-end. De esta manera, lograron combinar características de ambas arquitecturas para obtener los beneficios deseados.

NVIDIA Tegra K1 Denver

Mediante el uso de un decodificador de hardware y un traductor binario de software, este procesador tiene la capacidad de convertir instrucciones ARM en instrucciones nativas de microcódigo. Este proceso de traducción permite ejecutar de manera efectiva y eficiente el software diseñado para la arquitectura ARM en este procesador.

Recuerda que mejorar la compatibilidad con varias arquitecturas se logra mediante capas de software afecta al rendimiento, pero la implementación por hardware tampoco es la más eficiente. Lo ideal es usar la misma ISA.

¡No olvides comentar!