El filtrador es @momomo_US, quien ha desvelado los próximos AMD EPYC Milan-X con arquitectura Zen 3 y que contaría con un empaquetado 3D Chiplet. Llegarían antes que los chips de servidores EPYC Zen 4 (Genoa), así que podríamos verlos entre 2021 y 2022.

De momento, AMD ya ha confirmado que llegará 3D V-Cache, una tecnología de apilado, a su arquitectura Zen 3. Sin embargo, no vemos dicha tecnología en los Zen 3 corrientes, así que podríamos ver una pequeña variante de Milan llamada «Milan-X», caracterizada por incorporar este apilado, ¿o no?

Se filtran los SKU de AMD EPYC Milan-X, ¿3D V-Cache a la vista?

EPYC 73○○X

(੭ु´・ω・`)੭ु⁾⁾— 188号 (@momomo_us) August 25, 2021

La noticia versa sobre la filtración de los SKU de los próximos EPYC Milan-X de AMD, unos procesadores de servidores que vendrán con arquitectura Zen 3, hasta 64 núcleos, cuya novedad radica en el uso de 3D V-Cache. En principio, los primeros chips en disponer de la tecnología de apilado 3D V-Cache serían los Ryzen Zen 4, que vendrían a finales de este mismo año.

¿Seguro? A mí no me queda tan claro porque los EPYC Milan-X se lanzarán antes de los EPYC Genoa (Zen 4), y los últimos vienen entre 2022-2023, por lo que tienen que presentarse antes de la próxima generación. Estos chips basados en Zen 3 no serían una nueva familia, sino que tendrían una mejora respecto a Milan.

Esta filtración se centra en 4 AMD EPYC Milan-X:

- EPYC 7773X con 64 núcleos (100-000000504).

- EPYC 7573X con 32 núcleos (100-000000506).

- EPYC 7473X con 24 núcleos (100-000000507).

- EPYC 7373X con 16 núcleos (100-000000508).

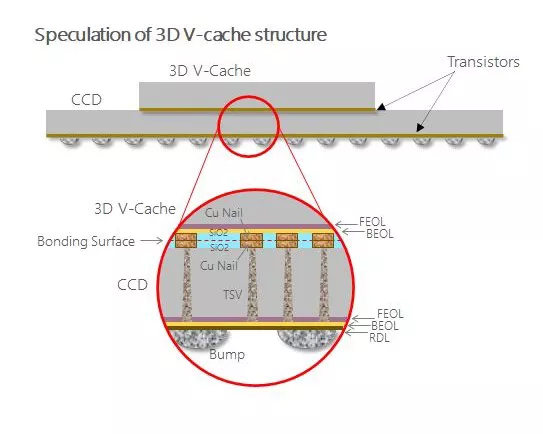

Es inevitable hablar de CCD y del nivel de apilamiento porque los 4 EPYC que han surgido llevan los mismos núcleos que los actuales, así que el apilamiento de CCD no llegará de momento. La fuente apunta esto porque los CCD vienen con su caché integral, aunque integraría una caché SRAM mediante el apilamiento del chiplet.

Hasta ahora, la tecnología 3D V-Cache se implanta a través del Micro Bump y de las interconexiones TSV. Toda esta tecnología se ha diseñado en colaboración con TSMC porque, al final, son los taiwaneses quienes van a fabricar los chips.

Para que os hagáis una idea, una pila 3D V-Cache tiene 64 MB L3 de caché, sumándose a los 32 MB que tiene ya el chip para lograr un total de 96 MB/CCD. AMD aseguró que se puede llegar a la cifra de 512 MB caché L3 por CCD, por lo que con 64 MB L3 se puede llegar a 768 MB L3 (8 pilas de CCD V-Cache 3D = 512 MB).

Entonces, ¿solo mejora la implementación de 3D V-Cache? Bueno, se habla de unas frecuencias más altas en los chips, y se habla de que ya es un «hito» relevante el hecho de que sean los primeros chips en introducir esta tecnología de apilamiento.

Desde luego que van a ser «los conejillos de indias» de AMD, aunque la mayoría de especificaciones son las mismas que Milan: mismo socket, plataforma, proceso de TSMC, TDP, etc.

Te recomendamos los mejores procesadores del mercado

¿Qué te parece esta tecnología de apilado? ¿Consideráis qué va a ser crucial en servidores y centros de datos?