La entrega de potencia en los procesadores más complejos está siendo todo un reto. En su día también lo fue la entrega de señal de reloj para la frecuencia, que pasó de entrar la señal por unos pines a tener una compleja distribución en árbol para llegar a todas las unidades funcionales o núcleos de forma más pareja y sin problemas de retrasos. Por eso, voy a dedicar este artículo a esta entrega de potencia y cómo la están resolviendo las compañías tecnológicas.

Índice de contenidos

Introducción

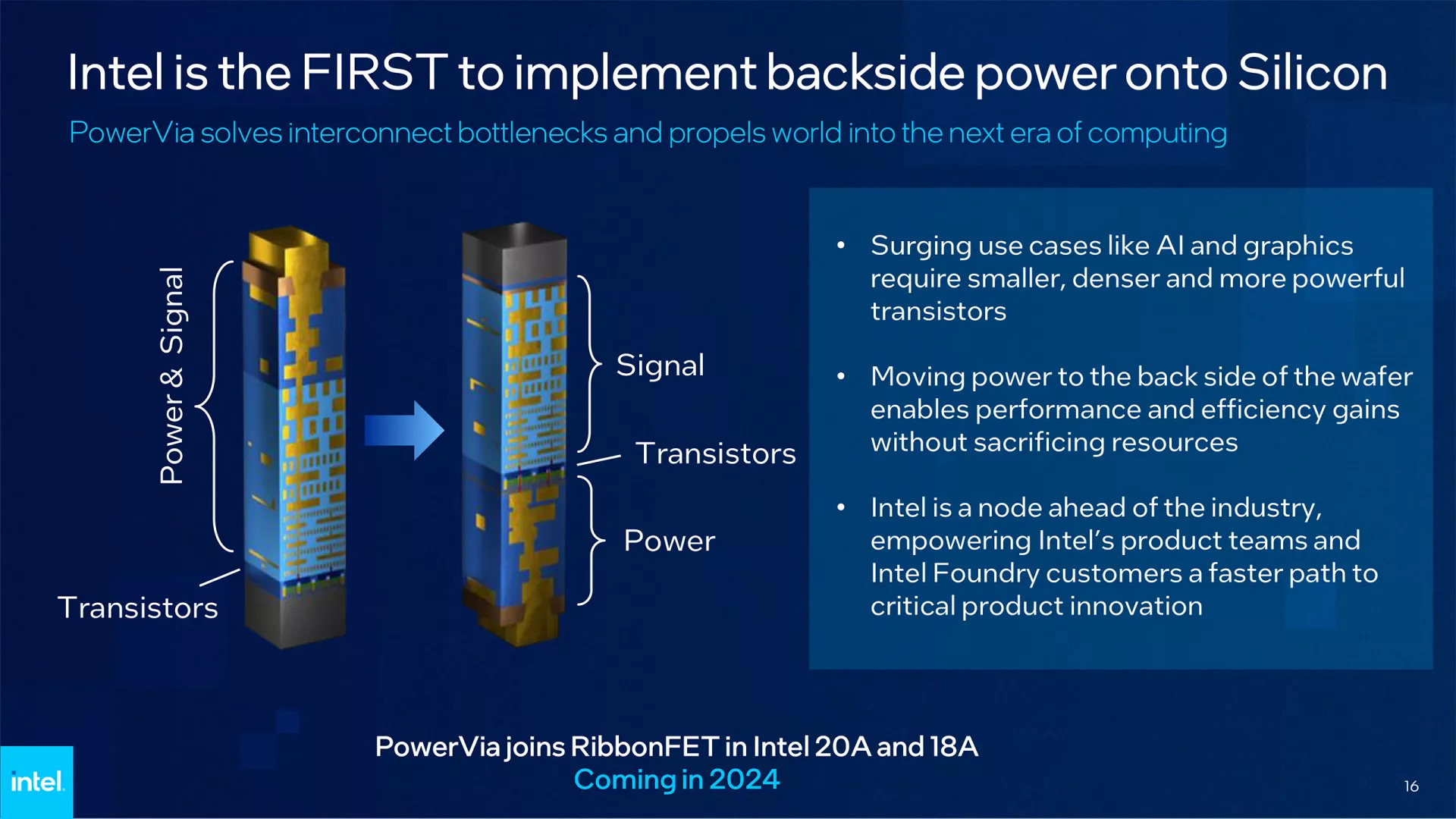

Algunas compañías que desarrollan procesadores de alto rendimiento, como CPUs y GPUs avanzadas, entre otros, están buscando nuevas formas de entregar la potencia necesaria para que el chip funcione de manera más eficiente. Intel es una de estas compañías, y que empleará una Backside Power Delivery Network (BD PDN) y PowerVia, es decir, una red de entrega de energía trasera para sus nodos posteriores a Intel 4. Pero…¿qué es eso de PowerVia y PDN? Pues bien, vamos a ver cómo estas novedades pueden ayudar a solucionar algunos problemas actuales.

¿Qué es PDN?

Las tecnologías de fabricación 18A y 20A de Intel introducirán dos avances significativos: los transistores RibbonFET, es decir, como Intel llama a sus GAAFET, y la red PowerVia, un tipo de suministro de energía en la parte trasera o BD-PDN de forma genérica.

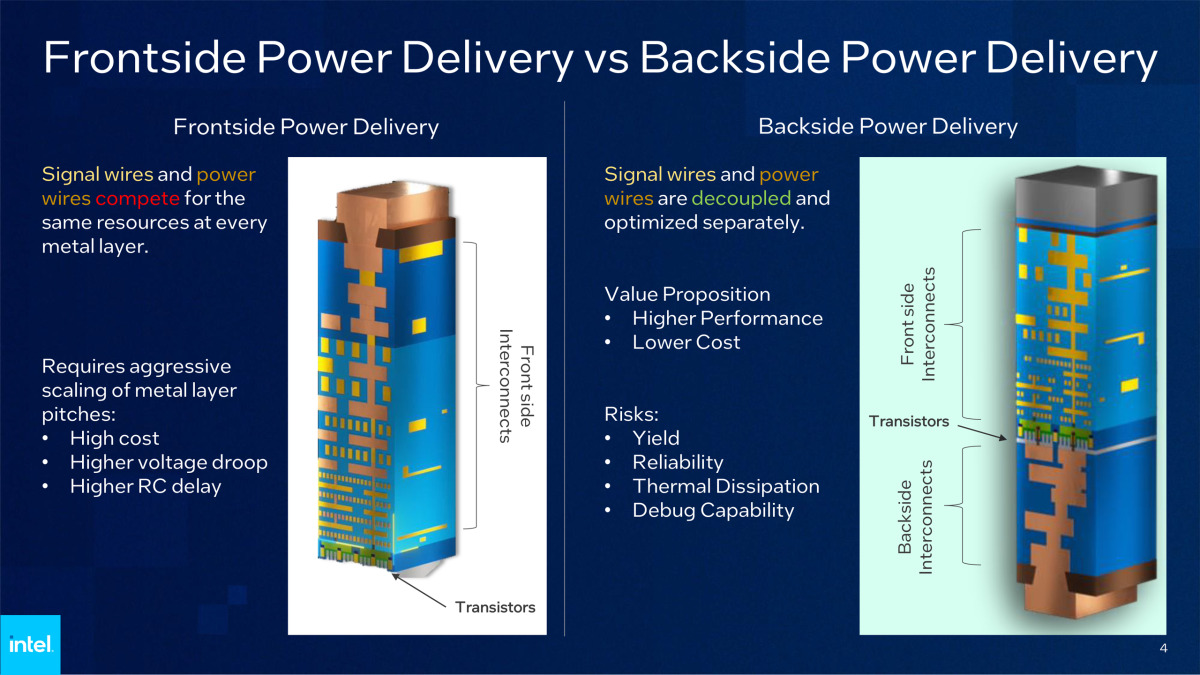

El objetivo del BD-PDN es separar la alimentación y el cableado de entrada/salida (datos), moviendo las líneas de alimentación hacia la parte posterior del chip. Gracias a eso se abordan problemas como el incremento de resistencias en la etapa posterior de la línea (BEOL), lo que se traducirá en un incremento del rendimiento y bajada de consumo de los transistores.

Además, elimina posibles interferencias entre las interconexiones de datos y de alimentación, y aumenta la densidad de los transistores lógicos. Como sabes, éste era otro de los grandes problemas en la alimentación por la parte superior del chip, ya que las interferencias podían alterar los resultados de la información que viajaba por estas vías, produciendo errores, y los fabricantes tenían que poner soluciones de aislamiento cada vez más costosas y complejas.

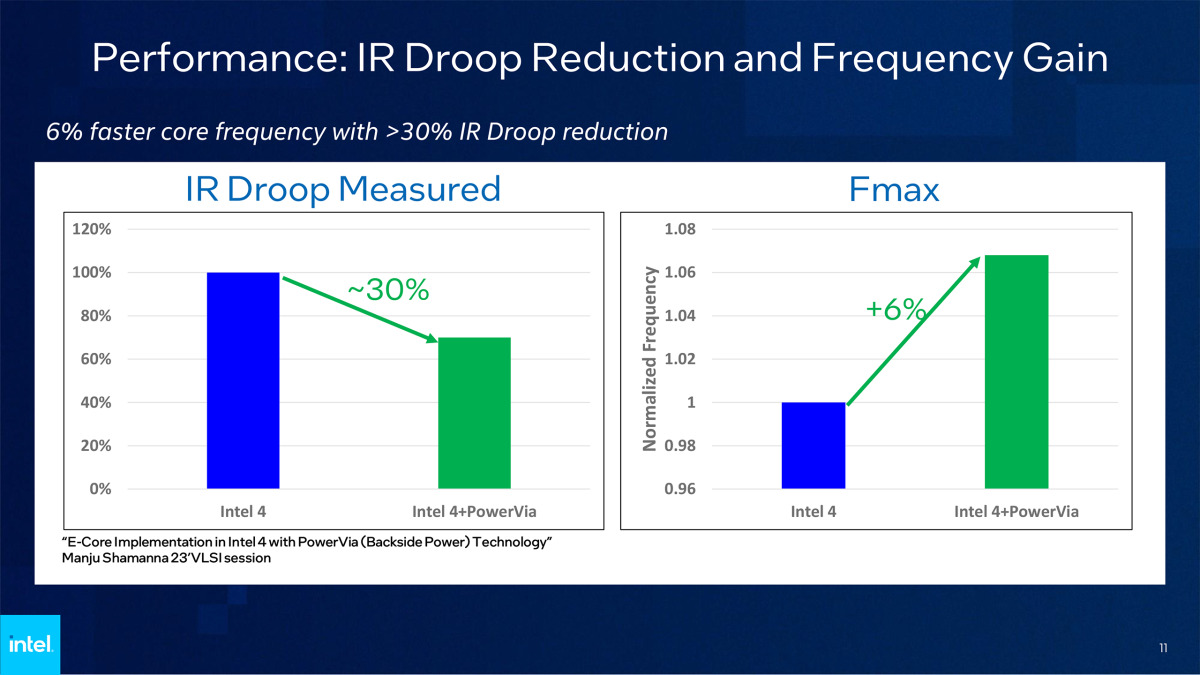

Con el tiempo, PDN se convertirá en un estándar en los chips, pero por ahora el primero en anunciarlo y ponerlo en marcha ha sido Intel, aunque le seguirán seguramente otros como TSMC y Samsung, ya que las mejoras son notables como se puede apreciar en la siguiente imagen:

Como se aprecia, según los análisis de la propia Intel, cuando se emplea PowerVIA, es decir, la BD-PDN de Intel, se puede aumentar la velocidad de reloj en más del 6%, reduce la caída de voltaje IR en un 30% y aumenta la densidad de las celdas a más del 90%. Sin embargo, no todo son ventajas, también supone un gran desafío poder implementar esta entrega de potencia trasera para los procesadores.

¿Cómo se implementa PowerVia?

La implementación de una red de suministro de energía (PDN) en la parte trasera es notablemente diferente a la tradicional entrega de energía en la parte frontal. La producción de chips, incluso los más avanzados, es relativamente sencilla en la actualidad, pero no es así con la BD-PDN.

Con BD-PDN, el proceso de fabricación de cada oblea comienza con la capa M0, la más pequeña de todas las capas de metalización. En procesos actuales, estas conexiones metálicas tienen muy pocos nanómetros, y necesitan de procesos sofisticados de EUV para su creación en los modernos procesadores. Luego, los fabricantes de chips usan un sustrato para crear las capas de transistores sobre la M0, y van aumentando gradualmente los tamaños para conectar todas las capas y alimentar los transistores. Es decir, al revés del proceso convencional.

Las interconexiones de entrada/salida, se enrutarán de forma convencional, es decir, en la parte frontal del chip, como se puede apreciar en las imágenes anteriores. Pero ahí ya no habrá interconexiones de potencia, por lo que se permitirá aumentar también el E/S del chip al disponer de más superficie, y se evitarán esas interferencias que he comentado antes.

El proceso de fabricación de una oblea con PowerVia BS PDN de Intel implica producir todas las capas lógicas complejas y las interconexiones de señal, y luego dar la vuelta a la oblea y construir la red de suministro de energía «sobre» la lógica. En teoría, este giro puede parecer algo simple, pero en realidad agrega muchos pasos al proceso, como eliminar el exceso de silicio de la oblea para construir el PDN sobre los transistores lógicos, limpieza de CMP, metrología, litografía y grabado, entre otros. Y eso encarecerá los chips, sí, afectará también a tu bolsillo hasta que no madure y baje de precio.

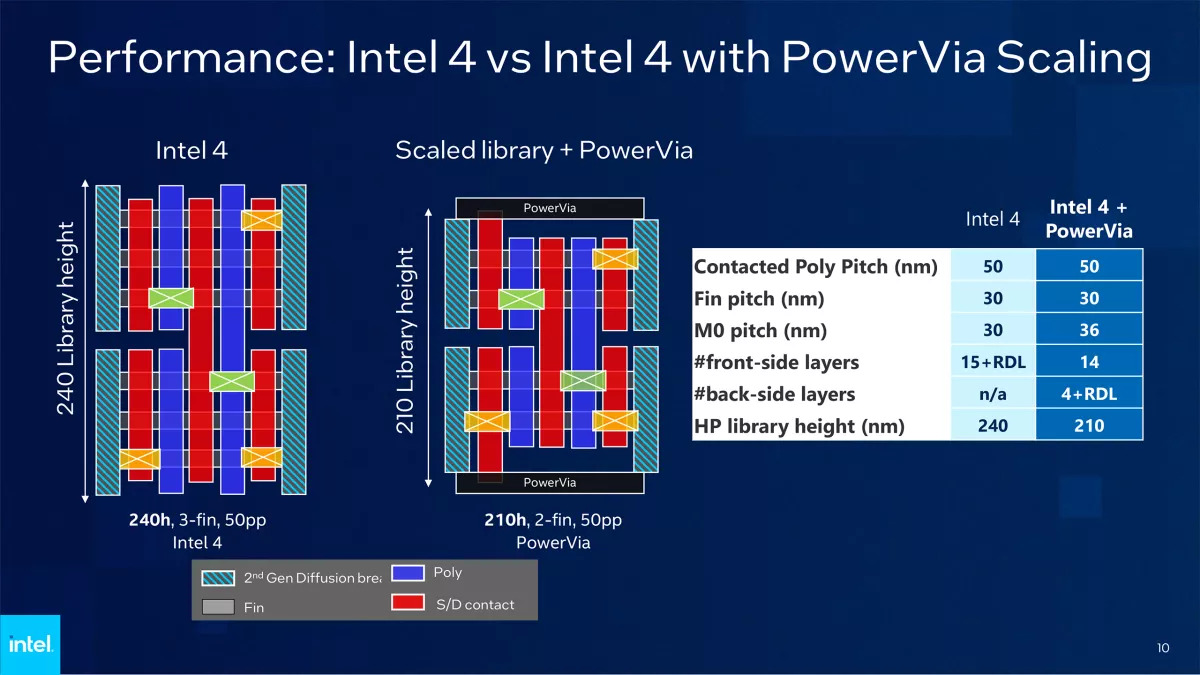

Es decir, es posible que un ciclo de proceso de este tipo no requiera las herramientas más avanzadas de la fábrica, pero aún conlleva costes. De hecho, según una diapositiva de Intel, la tecnología de proceso Intel 4 utiliza 15 capas metálicas y una capa de redistribución (RDL), mientras que Intel 4 + PowerVia utiliza 14 capas laterales frontales, cuatro capas laterales traseras y una RDL, lo que incrementa el número total de capas a 18+RDL. Traducido, es probable que Intel suba los precios de sus unidades o que los venda con márgenes de beneficio inferiores, aunque ya veremos…

Qué tener en cuenta sobre los procesadores BD PDN que llegarán

Existen diversos aspectos a tener en cuenta en relación con una red de suministro de energía (PDN) en la parte trasera:

- Esta implementación implica un cambio drástico en el proceso de fabricación, lo cual llevó a Intel a buscar formas de garantizar altos niveles de rendimiento a pesar de los cambios radicales.

- Intel tuvo que asegurarse de que la BD PDN fuera igual de fiable que su PDN frontal actual y que funcionara según lo planificado.

- Dado que las interconexiones de entrada/salida y de alimentación ahora se encuentran en ambos lados de los transistores, la capa activa, se enfrentan desafíos adicionales para enfriar los procesadores en el futuro.

- La depuración de los chips se vuelve considerablemente más complicada, ya que debe eliminar las interconexiones de alimentación traseras para acceder a las capas de transistores.

- Al eliminar el exceso de silicio en la parte posterior de la oblea, se produce una pérdida de rigidez, por lo cual se utiliza una oblea portadora en el lado de la señal para mantener la estructura unida. Con el tiempo, esta oblea portadora también se adelgaza, pero su adición representa un paso de proceso complejo y probablemente necesario.

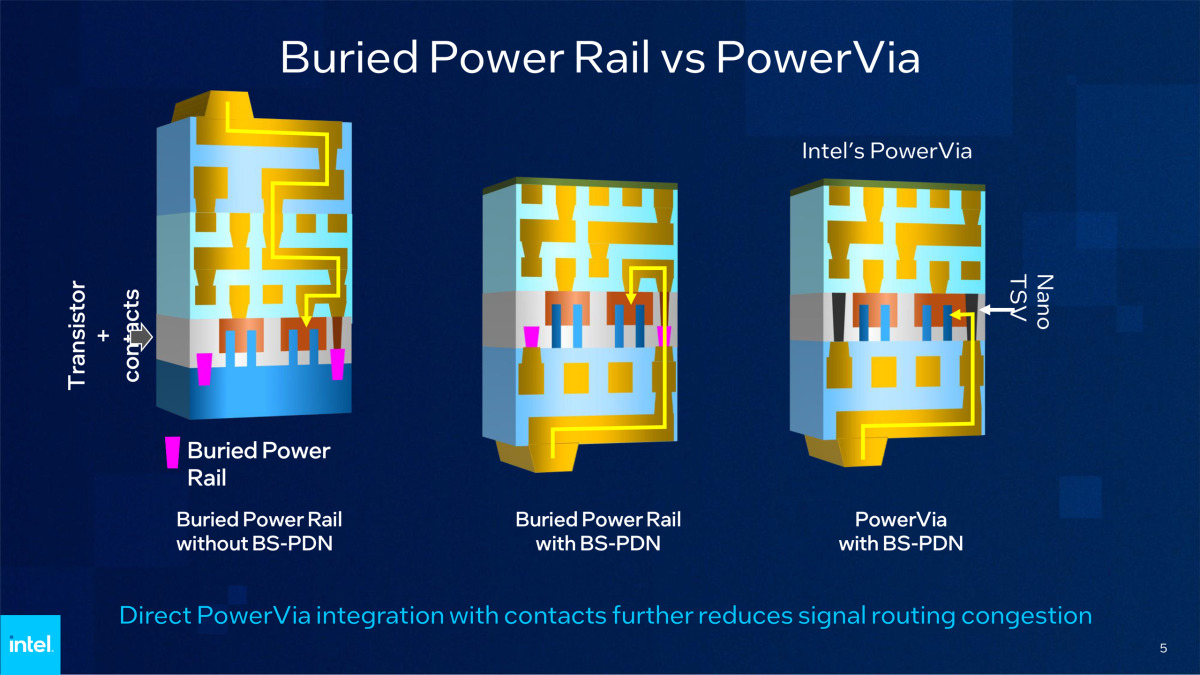

- No utiliza interconexiones de alimentación enterradas en el sustrato, sino que se basa en tecnología TSV para suministrar energía directamente a la capa de transistores, la misma que se usa para los empaquetados 3D. De hecho, el uso de estas vías es la razón por la cual la compañía ha denominado su tecnología como PowerVia.

Resultados preliminares en los procesadores

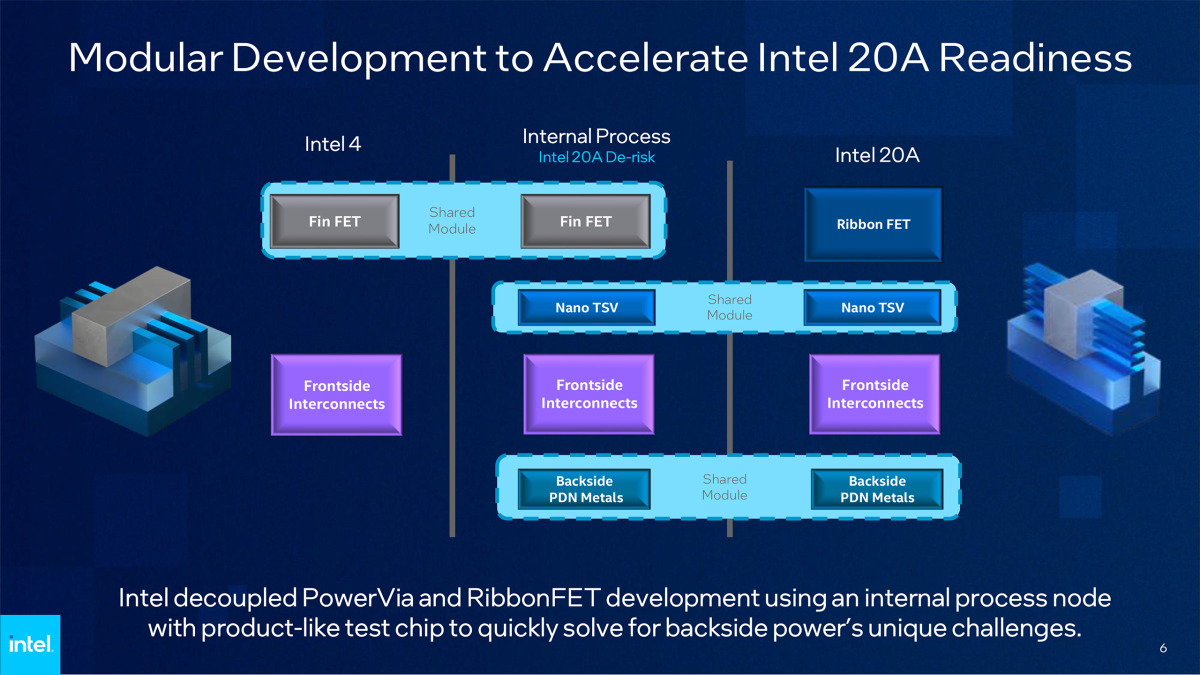

Dado que Intel ya no lidera de manera indiscutible el mercado de chips con las mejores tecnologías de proceso, la empresa no podía permitirse el riesgo de tener un punto potencial de falla en uno de sus nodos de próxima generación. Por lo tanto, separaron el desarrollo de los transistores RibbonFET GAA y PowerVia BS PDN para simplificar el proceso de desarrollo. Trabajaron en RibbonFET con una PDN convencional y luego depuraron PowerVia utilizando los probados transistores FinFET. Es decir, teniendo siempre un lado en lo convencional…

Para probar su red de suministro de energía en la parte trasera, PowerVia, Intel creó un proceso de fabricación especial basado en su nodo Intel 4. Este proceso utiliza transistores FinFET probados pero incorpora un riel de alimentación en la parte trasera en lugar del riel de alimentación tradicional. Esta implementación se conoce como Intel 4 + PowerVia y se utiliza en un chip de prueba llamado Blue Sky Creek.

El chip de prueba Blue Sky Creek de Intel cuenta con dos chips, cada uno con cuatro núcleos de bajo consumo basados en la microarquitectura Crestmont (E-Cores), es decir, es un chiplet. Estos núcleos están diseñados para operar a una frecuencia de 3 GHz con un voltaje de 1,1 voltios.

El propósito principal del chip de prueba es explorar las ventajas de PowerVia y eliminar los riesgos asociados con las futuras tecnologías de proceso 20A/18A antes de tener los primeros procesadores que lo implementen en producción. Esto incluye evaluar el rendimiento, la confiabilidad tanto de la PDN como del chip, la capacidad de enfriamiento y la depuración.

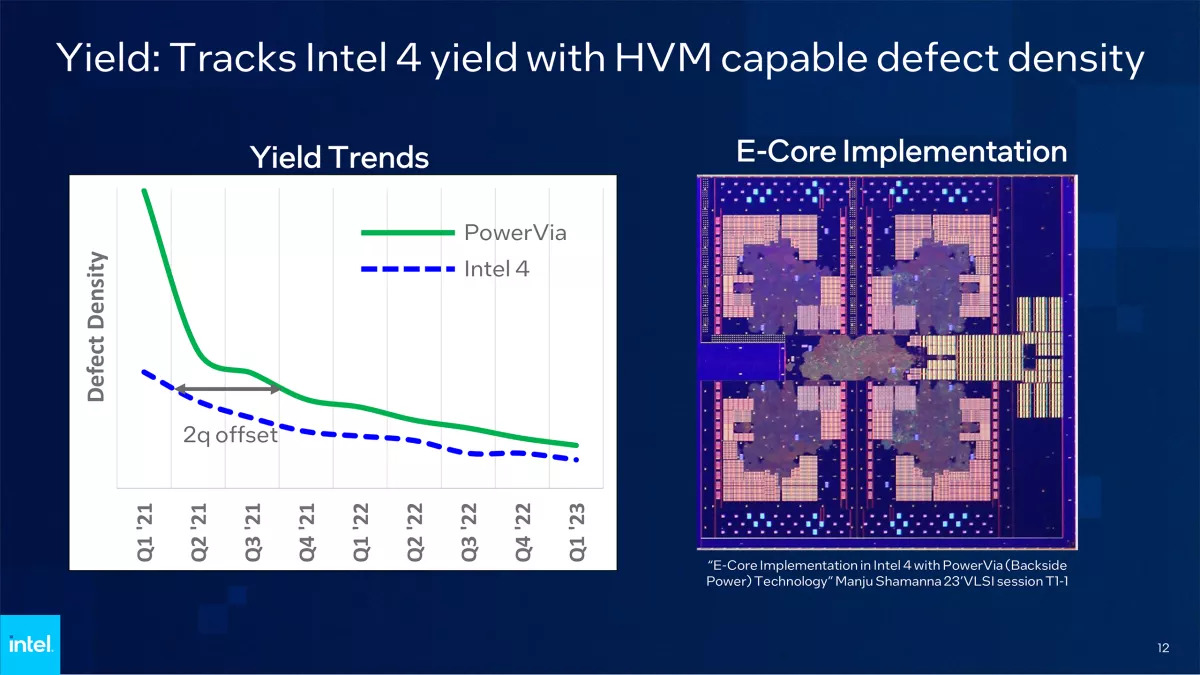

En cuanto a los resultados, la compañía Intel anunció que el yield es prácticamente el mismo que con Intel 4 convencional, aunque no sabemos hasta qué punto esto es cierto o se trata de marketing. Piensa que si el yield es malo, eso incrementará aún más los precios, lo que puede ser perjudicial para sus compradores.

Por otro lado, los objetivos de fiabilidad y las características de los transistores también se han cumplido según las expectativas requeridas para la producción. Además, las características térmicas del chip de prueba se ajustan a las expectativas. Sin embargo, Intel reconoce que la refrigeración será un desafío con la PDN trasera, por lo que han desarrollado nuevos enfoques de mitigación térmica para enfriar los chips de próxima generación.

La depuración podría considerarse como una de las partes más complicadas del proceso, pero afortunadamente, los ingenieros de validación de Intel encontraron una manera de superar las dificultades.

¿Cuándo llegará?

Intel tiene previsto lanzar sus nodos de proceso 20A y 18A, que utilizarán la tecnología de entrega de energía trasera PowerVia, en el segundo semestre de 2023 y el primer semestre de 2024, respectivamente. Los primeros procesadores para clientes fabricado en el nodo 20A serán los Intel Arrow Lake, cuyo lanzamiento está previsto para mediados de 2024 o finales de este.

Estas tecnologías de fabricación, tanto el nodo 18A como el 20A, están siendo desarrolladas tanto para los productos internos de Intel como para los clientes de Intel Foundry Services (IFS). Por lo tanto, PowerVia ofrece beneficios para terceros.

Pero solo el tiempo dirá si PowerVia BS PDN proporcionará beneficios tangibles. No obstante, parece ser que sí, y que será un estándar, la empresa TSMC, de hecho, espera ofrecer una tecnología similar a finales de 2026 o principios de 2027…

¿Qué opinas?