Imec ha revelado una hoja de ruta sobre los nodos de proceso que nos esperan desde hoy hasta el año 2036. Se trata de la empresa de investigación de semiconductores líder en el mundo, que ha hecho una presentación en el Future Summit celebrado en Amberes (Bélgica).

Imec revela los nodos de proceso por debajo de los 1nm y más allá

La empresa de investigación ha elaborado un informe sobre los nodos de proceso que se van a utilizar en semiconductores avanzados (CPUs, GPUs, SOCs, etc) hasta el año 2036, revelando lo que nos espera más allá de los 1 nm.

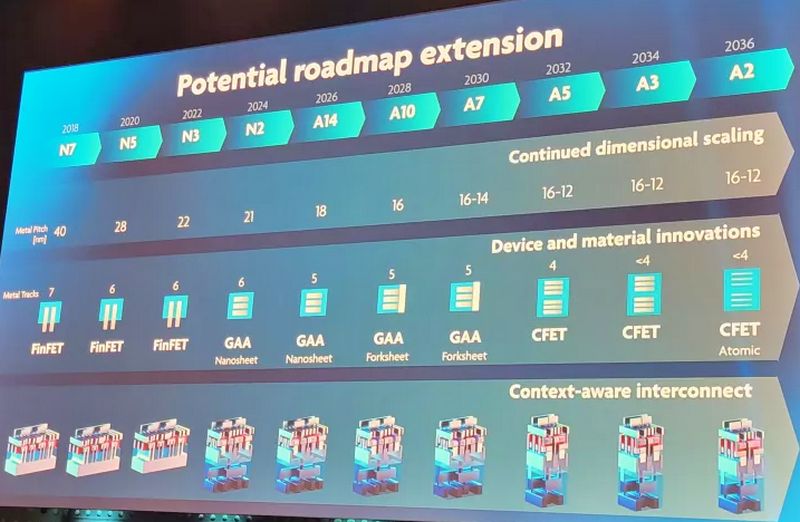

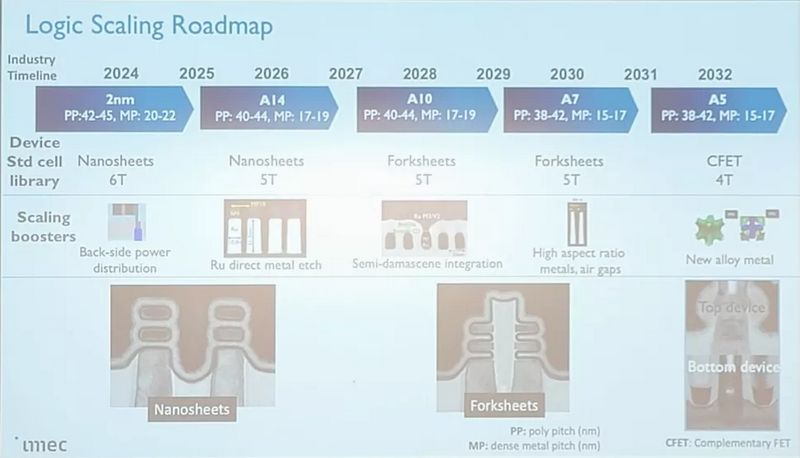

La hoja de ruta incluye diseños de transistores que evolucionan desde los transistores FinFET estándar que durarán hasta los 3nm, hasta los nuevos diseños de nanosheets y forksheet de Gate All Around (GAA) desde lo 2nm hasta los A7.

A partir de los 1 nm, los nodos de proceso pasarán a tener como medida los ‘angstroms’. Hay que tener en cuenta que 10 angstroms equivalen a 1 nm, por lo que los nodos más pequeños que 1 nm llegarán con los A7. Esto va a ocurrir a partir del año 2030.

Las diapositivas revelan nuevos tipos de transistores. Los transistores Gate All Around (GAA)/Nanosheet debutarán en 2024 con el nodo de 2 nm, sustituyendo a los FinFET que impulsan los chips avanzados actuales. Ya hemos visto anuncios de varios fabricantes de chips, como el RibbonFET de cuatro hojas de Intel, que incorporan diferentes variaciones de esta tecnología de transistores.

Imec espera que los transistores GAA/nanosheet y forksheet se utilicen hasta los nodos A7 (sub-1nm). A partir de allí, se van a utilizar los transistores FET complementarios (CFET), allá por el año 2032. Para el año 2036, la firma espera que se utilicen los transistores CFET con canales atómicos.

Te recomendamos nuestra guía sobre los mejores procesadores del mercado

Poder aumentar la densidad de transistores y reducir el tamaño de nodos será crucial para acelerar el rendimiento de la informática y añadir cada vez más características. Esto requería de mejoras en maquinaria que permitan crear chips más complejos con tamaños de transistores y comunicaciones super-diminutos.

Imec cree que la Ley de Moore se seguirá cumpliendo, planteando un reto a toda la industria, sobretodo por la llegada del aprendizaje automático. A medida que los nodos avanzan, la demanda de potencia aumenta y los costes se disparan. Este será un reto para la industria en los próximos años. Os mantendremos informados.