TSMC ha logrado un importante avance en el desarrollo de su nodo de proceso de 2nm. Los informes de este avance han aparecido en los medios de comunicación de Taiwán. Todo parece indicar que las primeras pruebas de fabricación de chips en 2nm comenzará en 2023 y que un año después comenzará a fabricarse en masa.

TSMC producirá en masa transistores MBCFET de 2nm en 2024

Actualmente, el último nodo de fabricación de TSMC es su proceso de 5nm de primera generación que se utilizará para construir los chips que dan vida a los smartphones insignia de Apple para el año 2020.

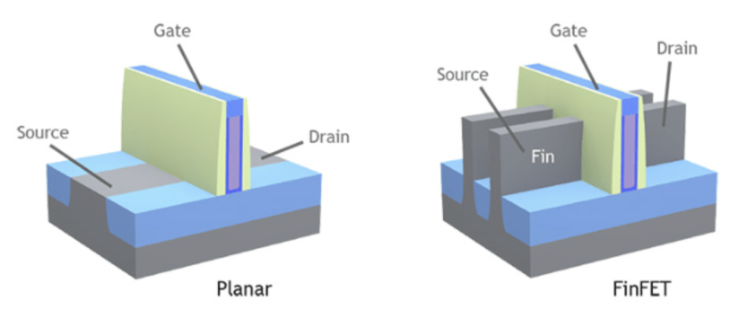

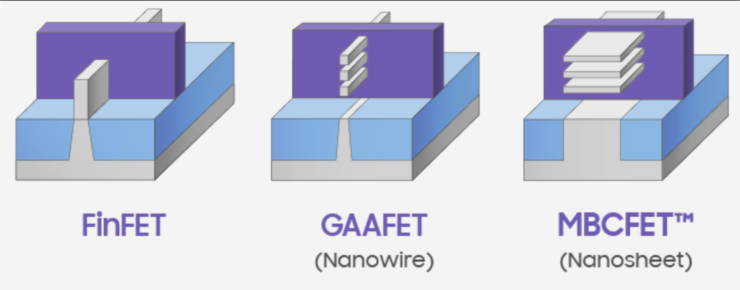

A diferencia del método ‘FinFET’ (Fin Field Effect Transistor), que es un término utilizado para describir el diseño de un transistor en los productos construidos por TSMC y Samsung, el proceso de 2nm de TSMC utilizará un diseño de transistor diferente. Este diseño se denomina transistor de efecto de campo de canal multi puente (MBCFET) y se suma a los anteriores diseños FinFET.

La decisión de TSMC de usar un diseño MBCFET para sus transistores no es novedosa. Samsung anunció el diseño para su proceso de fabricación de 3nm en abril del año pasado, y el diseño del MBCFET de la compañía fue una evolución sobre sus transistores GAAFET que desarrolló e introdujo conjuntamente con IBM en 2017. El MBCFET de Samsung, a diferencia de su GAAFET, utiliza una nano hoja para la fuente y el drenaje (el canal), mientras que el primero utiliza nanocables en su lugar. Esto aumenta la superficie disponible para la conducción y, lo que es más importante, permite al diseñador añadir más compuertas al transistor sin aumentar la superficie lateral.

TSMC espera que la tasa de rendimiento de su nodo de proceso de 2nm alcance un asombroso 90% en 2023. Si esto ocurre, entonces la fábrica estará bien encaminada para refinar sus procesos de fabricación y pasar cómodamente a la producción en volumen y en masa en 2024.

Visita nuestra guía sobre los mejores procesadores del mercado

[irp]Samsung, en el momento de su anuncio del MBCFET, había declarado que esperaba que los transistores de 3nm redujeran el consumo de energía en un 30% y un 45% respectivamente y mejoraran el rendimiento en un 30% con respecto a los diseños de 7nm, el paso a los 2 nm debería mejora estos números. Os mantendremos informados.