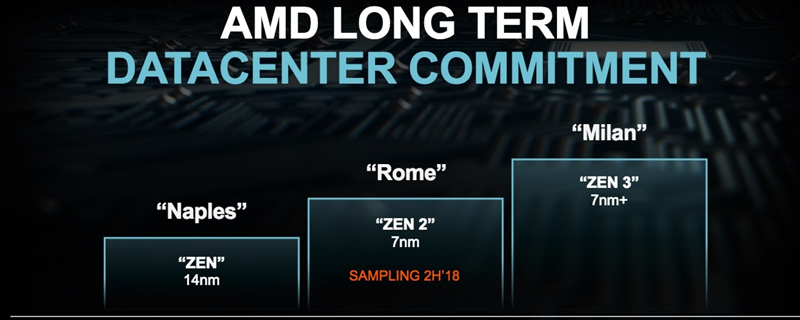

AMD reveló algunos detalles sobre la arquitectura EPYC Milan (Zen 3) y la arquitectura EPYC Génova (Zen 4) planificada por la compañía.

EPYC Milan y Génova, AMD da detalles sobre sus nuevos CPUs de servidores

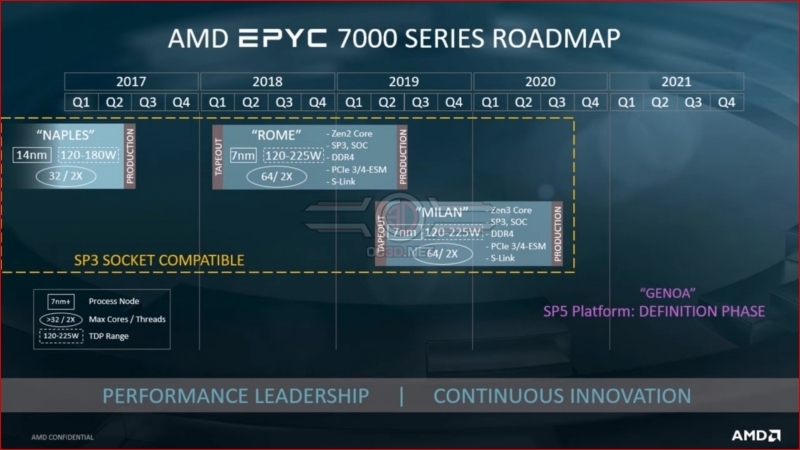

Durante su presentación, Martin Hilgeman de AMD, Senior Manager de aplicaciones HPC, reveló diapositivas que confirman que la próxima serie de procesadores EPYC ‘Milan’ se lanzará en el socket de servidor SP3 existente de AMD, soportará memoria DDR4 y ofrecerá el mismo TDP y las mismas configuraciones de núcleos que la serie de procesadores Rome.

Esta diapositiva parece disipar los rumores de que AMD planeaba lanzar Milán con una implementación 4x SMT, que alegaba que Zen 3 ofrecería a los usuarios cuatro hilos por núcleo de CPU. Parece que la principal fuente de mejoras en el rendimiento de Zen 3 vendrá de las mejoras en el IPC y de las ganancias en la velocidad del reloj, en lugar de los aumentos en el número de núcleos y de hilos. Con suerte, esto significa que Zen 3 se centrará en el rendimiento ‘mono-núcleo’ y en las mejoras de la arquitectura central.

Visita nuestra guía sobre los mejores procesadores del mercado

Pasando al EPYC Génova (Zen 4), Helgeman afirma que el Zen 4 está todavía en fase de diseño, lo que significa que los fabricantes de servidores y otros clientes tienen la oportunidad de influir en el diseño de Génova. También se confirma que esta nueva arquitectura se lanzará con un nuevo socket SP5, soportará un nuevo tipo de memoria (probablemente DDR5) y ofrecerá a los usuarios «nuevas capacidades», que no han sido reveladas.

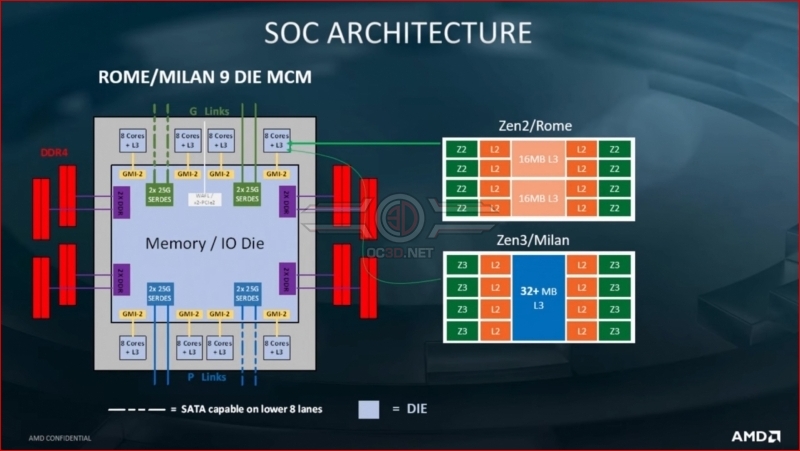

Interiorizando en el diseño de Zen 3, AMD confirmó que Zen 3 se alejaría del diseño de caché dividido de Zen/Zen 2, que dividía la caché L3 de la CPU de AMD entre dos CCX de cuatro núcleos. Esto significa que AMD podría estar alejándose de su propio diseño CCX de cuatro núcleos, creando un diseño CCX de ocho núcleos con Zen 3 o un diseño diferente.

[irp]En lugar de ofrecer dos cachés L3 de 16 MB (como se ve en el actual diseño Zen 2 de AMD), el diseño Zen 3 de AMD ofrecerá una combinación de «32+MB» de caché L3 entre los ocho núcleos de la CPU. Esto reducirá las latencias potenciales entre los núcleos de la CPU en un solo troquel y garantizará a los núcleos de la CPU un mejor acceso a la memoria caché L3 integrada. Además, esta cache seria más grande que la vista en generaciones anteriores.

EPYC Milan llegaría a nosotros durante el segundo semestre de 2020.