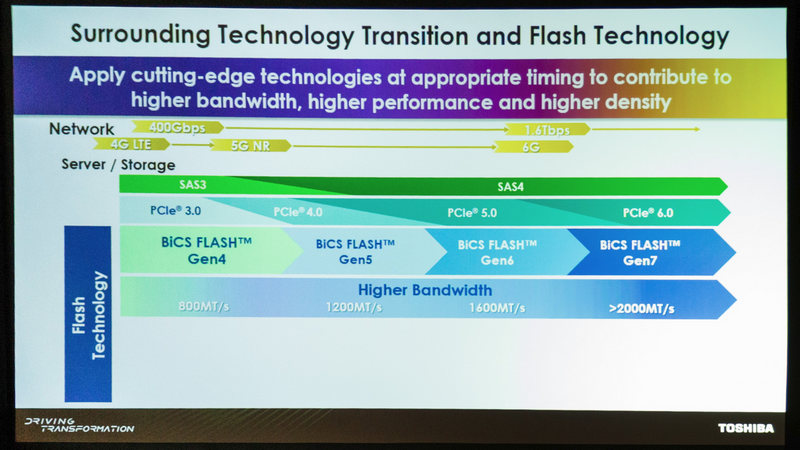

Toshiba ya ha comenzado a planificar las próximas generaciones BiCS Flash. Cada nueva generación coincidirá con las nuevas generaciones del estándar PCIe, comenzando con BiCS 5, que pronto saldrá al mercado en alineación con PCIe 4.0, pero la compañía no ha proporcionado un cronograma específico. BiCS5 tendrá un mayor ancho de banda de 1.200MT/s, mientras que BiCS6 alcanzará los 1.600MT/s, y BiCS7 está previsto que alcance los 2.000MT/s.

Toshiba ya desarrolla la tecnología Flash SSD de 5 bits por celda (PLC)

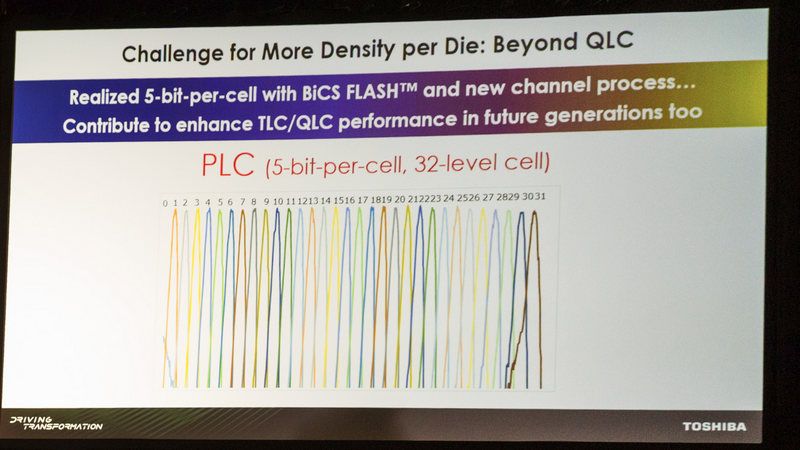

La compañía también ha comenzado a investigar sobre la tecnología flash NAND de celda de nivel Penta (PLC) y ha verificado el funcionamiento de la tecnología NAND de cinco bits por celda mediante la modificación de su actual NAND QLC. El nuevo flash proporciona más densidad con la capacidad de almacenar cinco bits por celda, en lugar de sólo cuatro que está presente en el QLC actual. Pero, para hacer esto, la celda necesita ser capaz de almacenar 32 niveles de voltaje distintos, y los controladores SSD necesitan leerlos con precisión. Con tantos niveles de voltaje para leer y escribir a escala manométrica, la nueva tecnología es un gran desafío. Para controlar los umbrales más estrictos, la empresa tuvo que desarrollar algunos procesos adicionales que podrían adaptarse a sus actuales TLC y QLC para aumentar el rendimiento.

QLC ya es bastante lento y tiene menor resistencia que otros tipos de flash. El PLC tendrá aún menos resistencia y un rendimiento más lento. Sin embargo, las nuevas funciones del protocolo NVMe, como Zoned Namespaces (ZNS), deberían ayudar a mitigar algunos de los problemas. ZNS por sí mismo tiene como objetivo reducir la amplificación de escritura, reducir la necesidad de aprovisionamiento excesivo de medios y el uso de DRAMs de controladores internos y, por supuesto, mejorar el rendimiento y la latencia.

Visita nuestra guía sobre las mejores unidades SSD del mercado

La empresa ha desarrollado un nuevo proceso que aumenta la densidad de matrices en las próximas generaciones de BiCS FLASH en todas sus formas. Esencialmente, dividirá la célula de memoria por la mitad para ampliarla mientras retiene el proceso de flash 3D normal. Toshiba no está segura de que este enfoque sea completamente factible en este momento.

Parece que el almacenamiento en unidades de estado sólido sigue en constante evolución, con unidades de mayor capacidad, más rápidas y más asequibles.