AMD volvió a la competitividad en el mercado de centros de datos con sus procesadores empresariales EPYC, que son módulos de hasta cuatro matrices Zeppelin de 8 núcleos. Cada matriz tiene su propio puente norte integrado, que controla la memoria DDR4 de 2 canales y un complejo de raíces PCI-Express gen 3.0 de 32 vías. En las aplicaciones que requieren un uso intensivo del ancho de banda de la memoria, este enfoque de la memoria no localizada presenta cuellos de botella en el diseño que se solucionarían en los nuevos Rome.

AMD EPYC Rome tendría un diseño de memoria monolítico

La familia de procesadores Ryzen Threadripper WX acentúa muchos de estos cuellos de botella, en el caso de aplicaciones de codificación de video que requieren mucha memoria, se ven caídas en el rendimiento a medida que las matrices sin acceso directo a E/S carecen de ancho de banda de memoria. La solución de AMD a este problema es diseñar la CPU muere con un Northbridge deshabilitado esta solución podría implementarse en sus próximos procesadores EPYC de segunda generación, cuyo nombre en código es «Rome«.

Te recomendamos la lectura de nuestro artículo sobre AMD Ryzen Threadripper 2990WX Review en Español

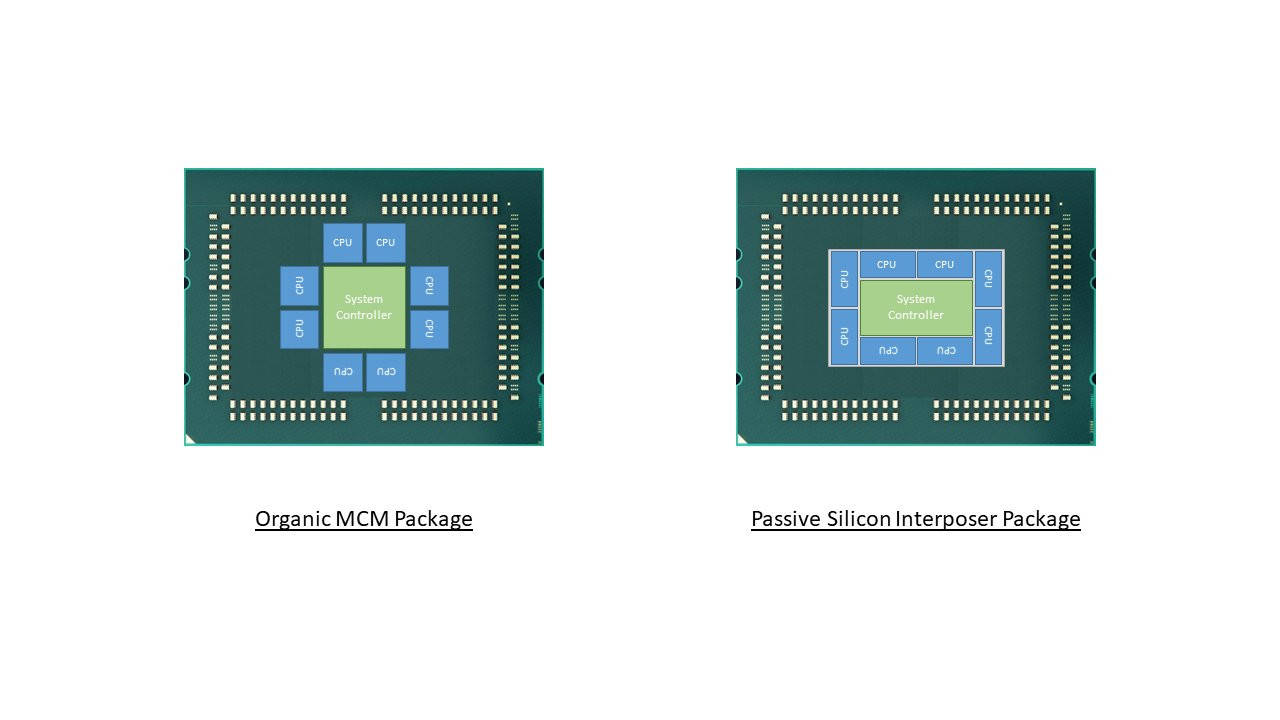

Los MCM de próxima generación de AMD podrían ver un diseño centralizado del controlador del sistema rodeado de dies, que podrían estar todos en un interposer de silicio, del mismo tipo que se encuentra en las GPU Vega 10 y Fiji. Un interposer es una matriz de silicio que facilita el cableado microscópico de alta densidad entre las matrices de un MCM. A diferencia de los procesadores EPYC de la generación actual, esta interfaz de memoria es verdaderamente monolítica, muy parecida a la implementación de Intel.

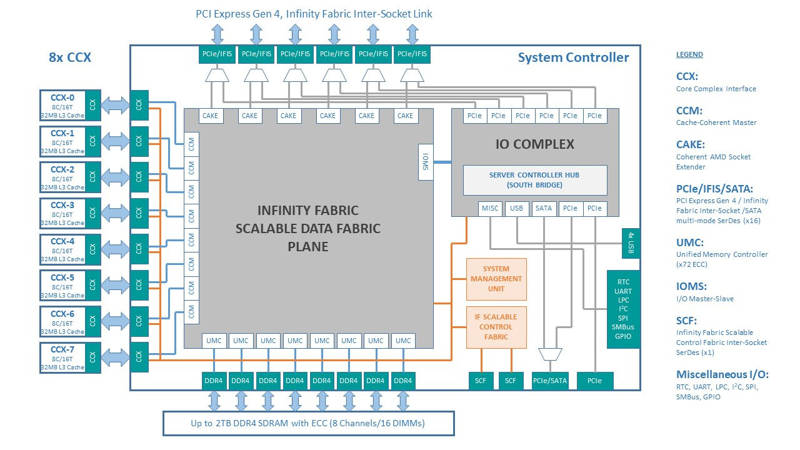

[irp]El controlador del sistema también cuenta con un complejo raíz PCI-Express gen 4.0 x96, que puede manejar hasta seis tarjetas gráficas con ancho de banda x16, o hasta doce en x8. La matriz también integra el southbridge, conocido como Server Controller Hub, que implementa interfaces de E / S comunes como SATA, USB y otras E / S heredadas de bajo ancho de banda, además de algunas otras líneas PCIe.